#### Table of Contents

| Chapter 4 | Power Conversion Circuits                             |  |  |

|-----------|-------------------------------------------------------|--|--|

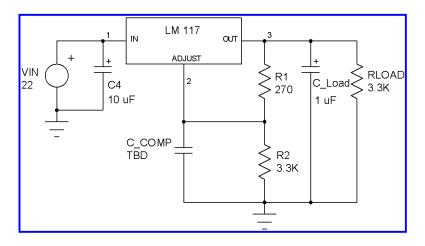

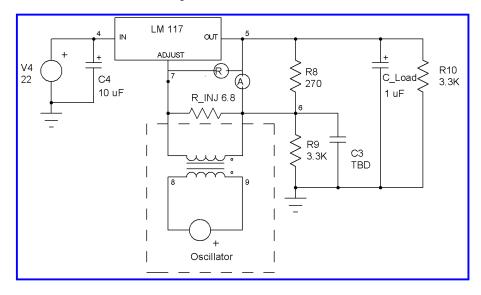

|           | 11 LM117 Three Terminal Linear Regulator              |  |  |

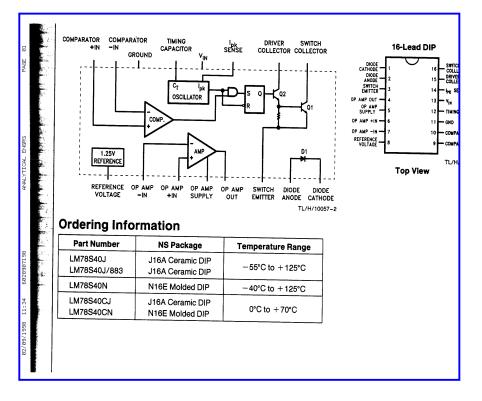

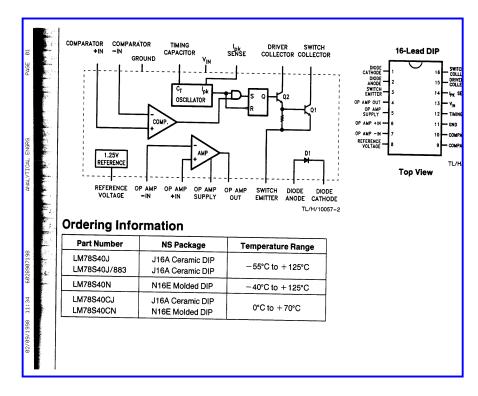

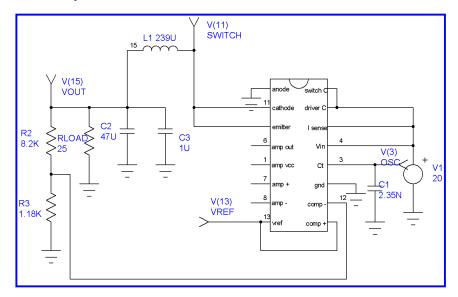

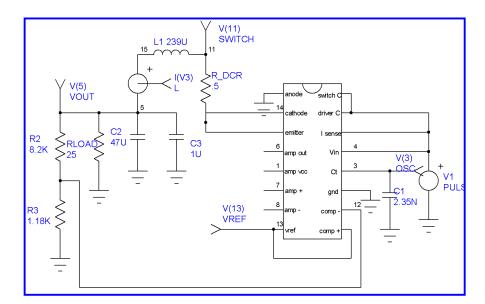

|           | 12 LM78S40 Simple Switcher DC to DC                   |  |  |

|           | 13 UA723 Hysteretic Converter                         |  |  |

|           | 14 1524 Buck Regulator                                |  |  |

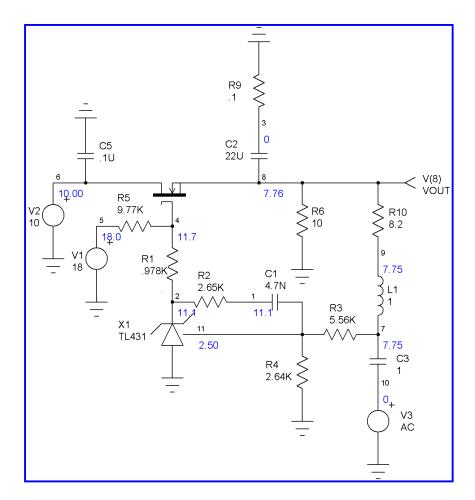

|           | 15 Low Drop Out Regulator                             |  |  |

|           | <u>16 STR 660</u>                                     |  |  |

|           |                                                       |  |  |

| Chapter 5 | Electronic Load Circuits                              |  |  |

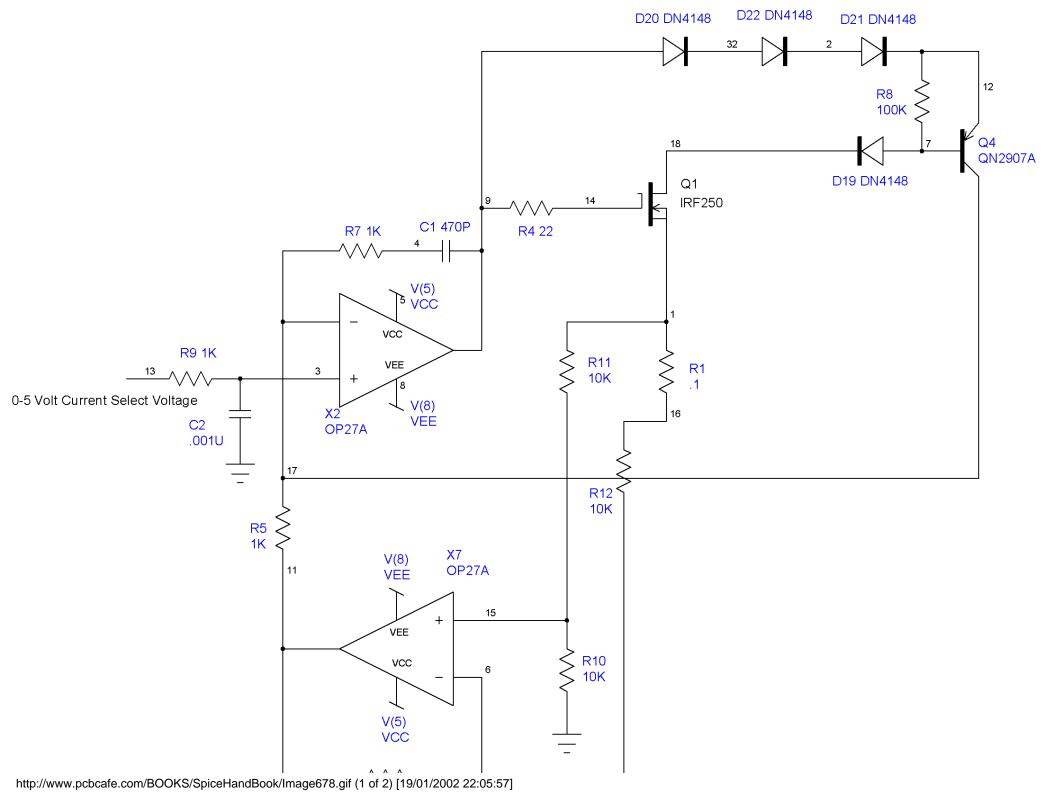

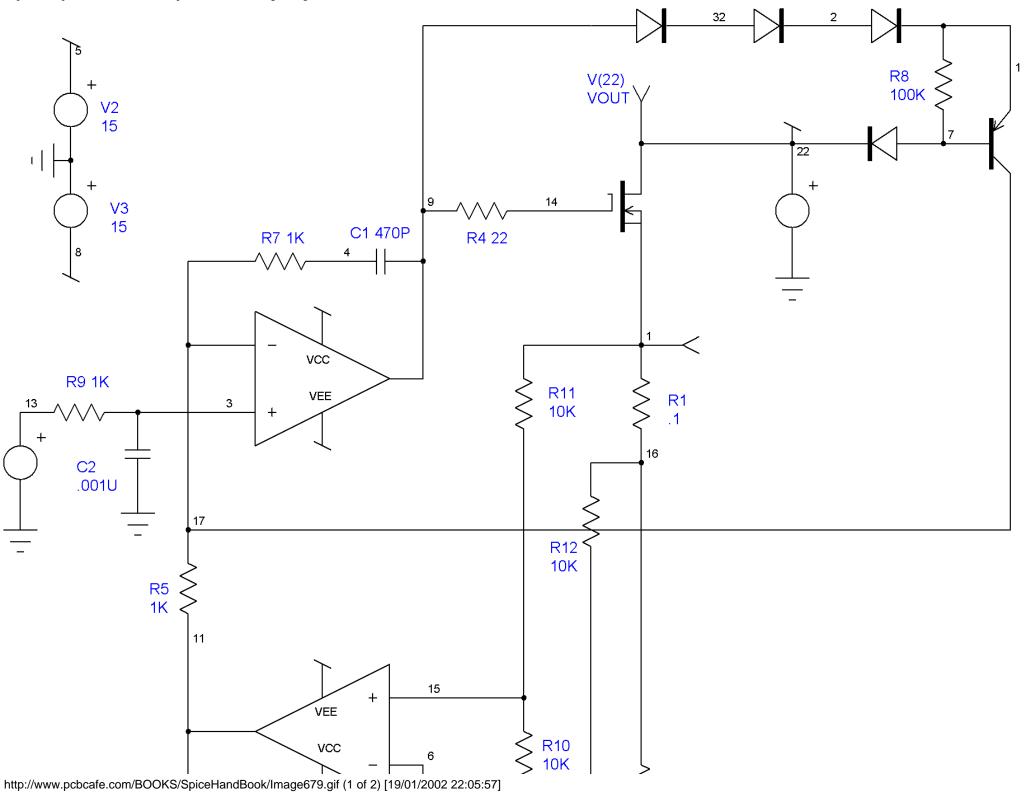

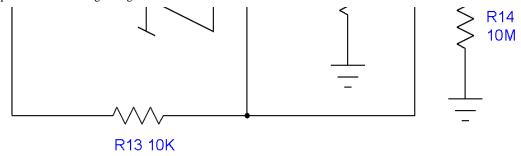

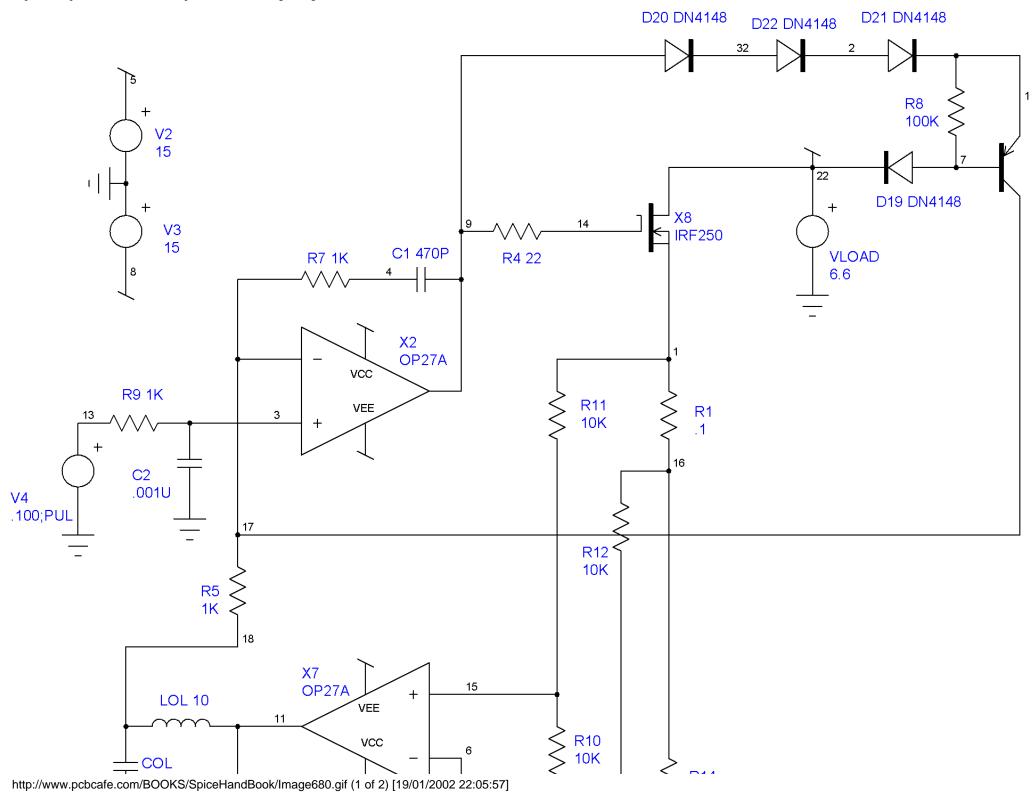

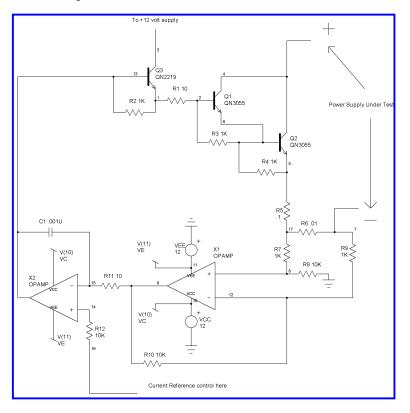

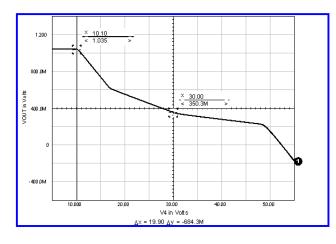

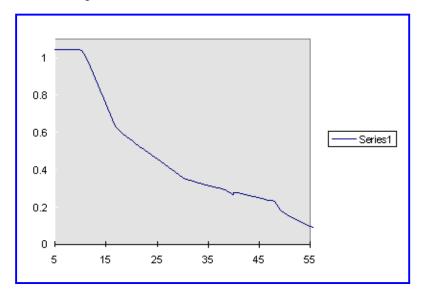

|           | 17 Power Section of an Electronic Load                |  |  |

|           | 18 Positive DC to Negative DC Comparator              |  |  |

|           | 19 Built in Variable Electronic Load                  |  |  |

|           | 20 Electronic Load using Power BJT Transistors        |  |  |

| Chapter 6 | Instrumentation                                       |  |  |

| Chapter 0 | 21 555 Timer                                          |  |  |

|           | 22 555 Missing Pulse Detector                         |  |  |

|           | 23 Operational Amplifier Adder                        |  |  |

|           | 24 Class AB Amplifier                                 |  |  |

|           | 25 Window Detector                                    |  |  |

|           | 26 Voltage Clamp                                      |  |  |

|           | 27 Resistance to Voltage Converter                    |  |  |

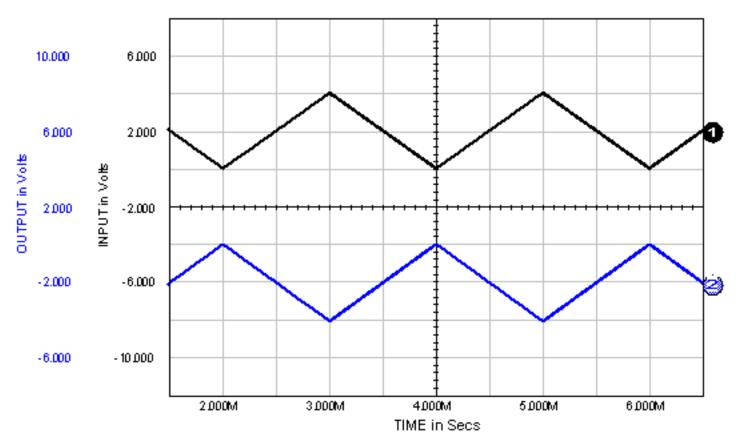

|           | 28 Polarity Gain                                      |  |  |

|           |                                                       |  |  |

| Chapter 7 | Logic Circuits                                        |  |  |

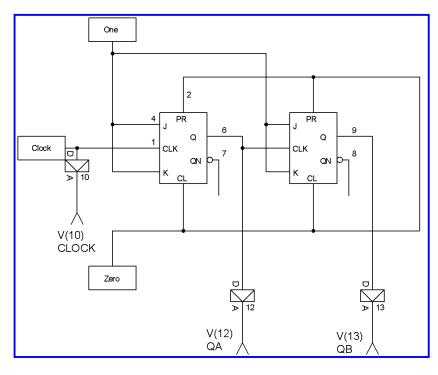

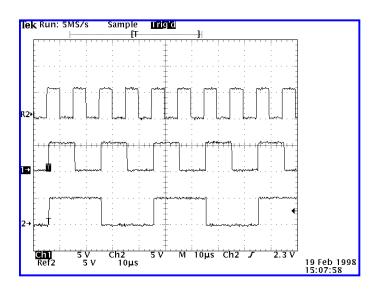

|           | 29 Binary Counter                                     |  |  |

|           | 30 Binary Decoder                                     |  |  |

|           | 31 Set Reset Latch                                    |  |  |

|           | 32 Stair Case Generator                               |  |  |

|           | 33 Phase Lock Loop                                    |  |  |

| Chapter 8 | Resonator/Oscillator Circuits                         |  |  |

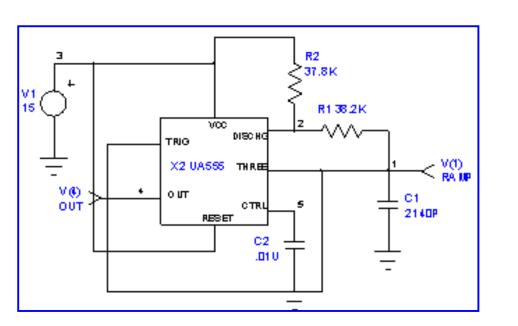

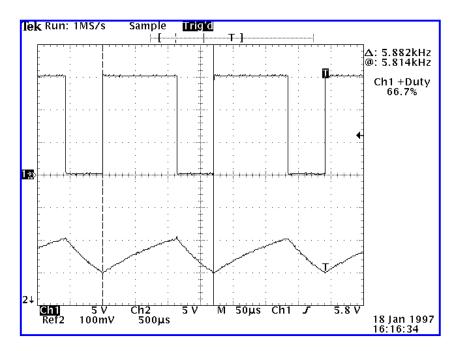

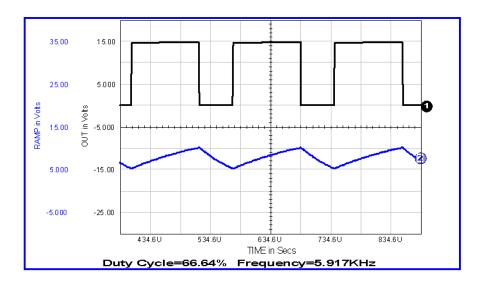

|           | 34 555 Timer Oscillator                               |  |  |

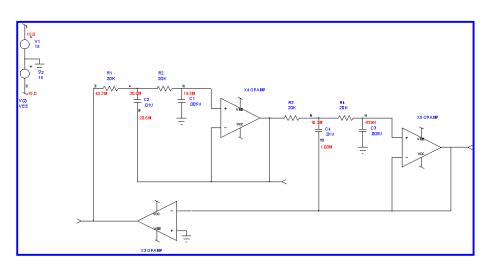

|           | 35 4 th_Order Butterworth Low Pass Oscillator         |  |  |

|           | 36 Hex Inverter Oscillator                            |  |  |

|           | 37 4 th Order Butterworth no Ofset Lowpass Oscillator |  |  |

|           | 38 Harmonic Neutralized Sine Wave                     |  |  |

|           | 39 Colpits Oscillator                                 |  |  |

|           | 40 Schmidt Trigger Oscillator                         |  |  |

|           | 41 LM111 Oscillator                                   |  |  |

|           |                                                       |  |  |

| Chapter 9 | Driver Circuits                                       |  |  |

|           | 42 UC1846 50% Duty Cycle Gate Drive                   |  |  |

|           | 43 Waveshaped                                         |  |  |

|           | 44 Zero-100% Duty Cycle                               |  |  |

Table of Contents

- Chapter 10 Voltage Multiplier Circuits

- 45 AC to DC Voltage Doubler

- 46 Cascade Doubler

- 47 Bridge AC to DC Doubler

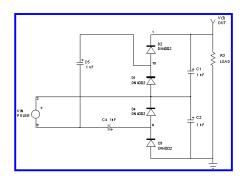

- 48 AC to DC Quadrupler

- 49 AC to DC Octupler

- 50 High Voltage High Current DC to DC

Acknowledgements

Expedition<sup>™</sup> Series

Large efforts seldom occur without assistance. The authors would like to graciously thank the efforts of those who, without their help, this book would not have been possible.

Andy Thompson from Spectrum, and Charles Hymowitz from Intusoft for providing full versions of their simulators for use in this book.

Steve Chapman, Editor at McGraw Hill for his guidance and support.

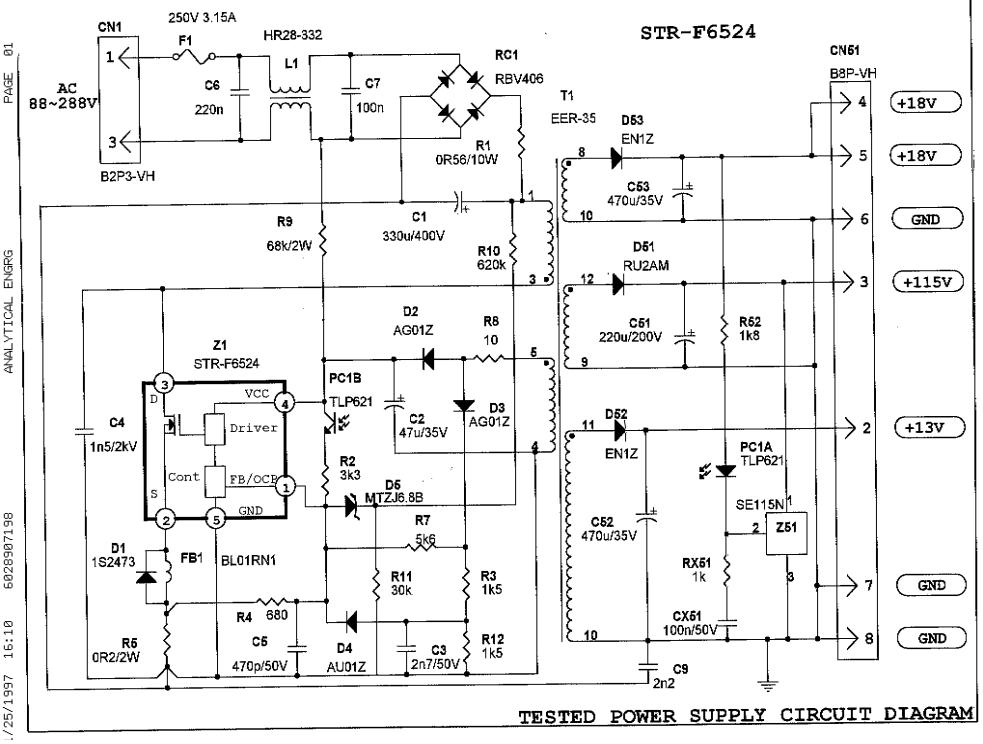

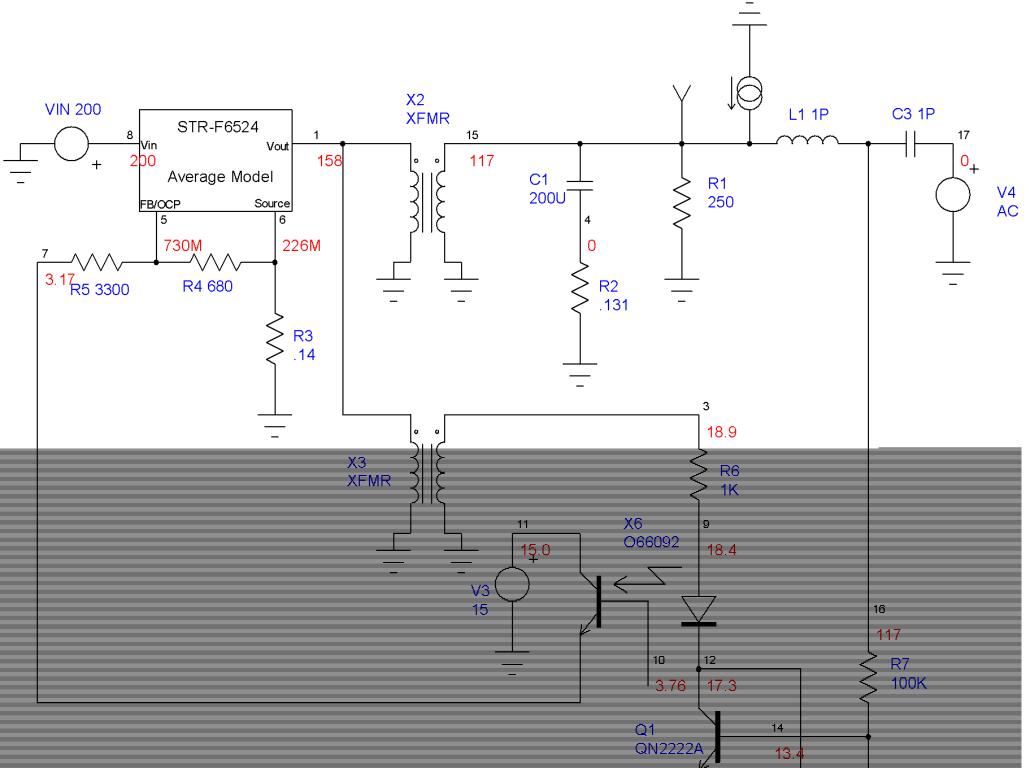

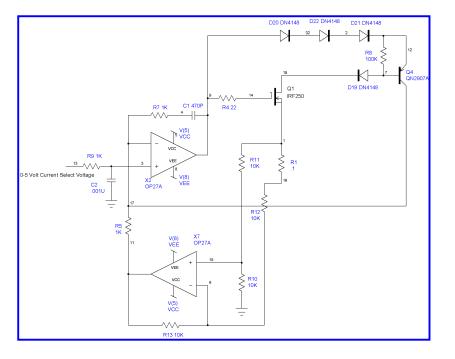

Paul Greenland from Allegro for providing STR 6600 data for use in the circuits of this book.

Barbara Sandler, for her patience, guidance, and management.

And to our customers, who keep us going.

To our loved ones:

Barbara, Shanna, and Rachel

Sonya and Kynlee

Nicolle

Acknowledgements

Karen, Barry, and Carole

#### Table of Contents

| Chapter 4 | Power Conversion Circuits                             |

|-----------|-------------------------------------------------------|

|           | 11 LM117 Three Terminal Linear Regulator              |

|           | 12 LM78S40 Simple Switcher DC to DC                   |

|           | 13 UA723 Hysteretic Converter                         |

|           | 14 1524 Buck Regulator                                |

|           | 15 Low Drop Out Regulator                             |

|           | <u>16 STR 660</u>                                     |

|           |                                                       |

| Chapter 5 | Electronic Load Circuits                              |

|           | 17 Power Section of an Electronic Load                |

|           | 18 Positive DC to Negative DC Comparator              |

|           | 19 Built in Variable Electronic Load                  |

|           | 20 Electronic Load using Power BJT Transistors        |

| Chapter 6 | Instrumentation                                       |

| -         | 21 555 Timer                                          |

|           | 22 555 Missing Pulse Detector                         |

|           | 23 Operational Amplifier Adder                        |

|           | 24 Class AB Amplifier                                 |

|           | 25 Window Detector                                    |

|           | 26 Voltage Clamp                                      |

|           | 27 Resistance to Voltage Converter                    |

|           | 28 Polarity Gain                                      |

| Chapter 7 | Logic Circuits                                        |

|           | 29 Binary Counter                                     |

|           | <u>30 Binary Decoder</u>                              |

|           | 31 Set Reset Latch                                    |

|           | 32 Stair Case Generator                               |

|           | 33 Phase Lock Loop                                    |

|           |                                                       |

| Chapter 8 | Resonator/Oscillator Circuits                         |

|           | <u>34 555 Timer Oscillator</u>                        |

|           | 35 4 th Order Butterworth Low Pass Oscillator         |

|           | <u>36 Hex Inverter Oscillator</u>                     |

|           | 37 4 th Order Butterworth no Ofset Lowpass Oscillator |

|           | 38 Harmonic Neutralized Sine Wave                     |

|           | 39 Colpits Oscillator                                 |

|           | 40 Schmidt Trigger Oscillator                         |

|           | 41 LM111 Oscillator                                   |

| Chapter 9 | Driver Circuits                                       |

| •         | 42 UC1846 50% Duty Cycle Gate Drive                   |

|           | 43 Waveshaped                                         |

|           | 44 Zero-100% Duty Cycle                               |

|           |                                                       |

Table of Contents

- Chapter 10 Voltage Multiplier Circuits

- 45 AC to DC Voltage Doubler

- 46 Cascade Doubler

- 47 Bridge AC to DC Doubler

- 48 AC to DC Quadrupler

- 49 AC to DC Octupler

- 50 High Voltage High Current DC to DC

Introduction

### Introduction

Since the introduction of SPICE in 1971, the simulation program has become one of the most popular analog simulation tools. In the last 10 years, we have seen explosive growth of SPICE, with the addition of SPICE 3 syntax, providing support for mixed mode simulation [Kielkowski, 1994]. We have also seen many new companies emerge as manufacturer's of SPICE simulation software, most of which is currently available for the PC platform.

Each vender of SPICE simulation software has added features, such as Monte Carlo functions, Schematic editor and Post Graphic processing, as well as substantial component libraries. In some cases, the manufacturers have modified the algorithms for controlling convergence and have added new parameters or syntax for component models.

We have also seen component manufacturer's providing their support. Many component manufacturer's provide models of components such as Mosfet's, transistors, Operational Amplifiers. Most of these models are available, free, via Internet Web sites.

The abilities of computers to model electronic circuits are increasing every day. The often quoted "Moore's Law" states that the speed of microprocessors doubles nearly every 18 months. As computers are becoming more powerful and more capable, computer simulation can become a more important tool in the design process.

Unfortunately, there is an unwillingness in the electronic design community to embrace the abilities of computers to model circuits. Many engineers still think of SPICE (Simulation Program of Integrated Circuit Electronics) simulation as a toy. The typical attitude of the design engineer, upon being shown a SPICE model of the impeding failure of his/her circuit will reply, "That's nice, but lets see what the hardware does." Even when the hardware fails, the engineer is more likely to investigate the charred and smoking breadboard than the SPICE model that predicted the result.

The purpose of this book is to show the abilities of SPICE and equivalent circuit simulation tools to accurately predict the behavior of electronic hardware circuitry. The emphasis of this book is on how well the simulation stacks up against real measured hardware. The uses of circuit simulation are well documented (Sandler 1996).

The speed a simulation can be performed is orders of magnitude faster than building the circuit on a lab breadboard.

The simulation can be run through any number of environments with ease.

Circuit tolerances and the effect on the operation of the functionality of the circuit can be easily evaluated.

There are still limitations to the capabilities of SPICE and similar circuit simulators. While the sophistication of simulation increases, the lab breadboard will still remain a necessary step in the design process. This book will aid the engineer in using SPICE simulation as a very powerful **tool** in the design process.

Simply, this book is a compilation of all manners of electronic circuits. Such compilations are not unusual, in fact, there are several excellent circuit encyclopedias on bookshelves. However, this book goes one step further. Instead of simply presenting the circuit to the reader, a SPICE schematic and the equivalent hardware performance is also provided, along with an explanation of the intricacies of the development of an accurate SPICE model for the circuit in question. This format benefits the reader in numerous ways. The reader can emulate the correlation techniques introduced in this book in order to make their own specific SPICE models accurately mimic the behavior of their hardware.

SPICE as a tool can give the design engineer a vast array of data that can ensure a successful and optimal design for their hardware. The designer has a hardware design that they know operates correctly, and they also have a SPICE model that can accurately reflect that designs behavior at the click of a mouse button. Clearly, SPICE modeling can be a much more integral step in the design process and prove its worth to engineers of any circuit discipline.

The book is structured intuitively, minimizing searching time and maximizing efficiency. The beginning of the book concentrates on the basics of computer simulation of circuits. An overview of the three most popular SPICE programs are provided, along with their differences and peculiarities.

We have selected a broad cross section of analog and mixed mode designs, which we have simulated as well as constructed. The circuits are grouped into logical chapters. Generic topics such as oscillators, amplifiers/receivers, power converters, filters, etc. all head their own chapter. Each chapter starts with a brief overview of the function of the circuits in that chapter. This is followed by each design type featured in this book that performs that function. For example, in the chapter on Reference Circuits, the beginning of the chapter details what reference circuits are and their uses in the system level. This is followed by a detailed discussion on a single type of reference circuit, the band gap reference.

Each circuit has a discussion of the theory of operation, followed by the SPICE model schematic, the simulation results, and a comparison to laboratory data. Advantages and disadvantages to each circuit are added, along with any tips or hints used to model the circuit accurately. We have attempted to perform each simulation using several manufacturer's versions of SPICE for comparison. Also included are the simulation run times for each circuit.

Three simulation programs were used to simulate the circuits in this book. IsSpice v7.6 $\odot$ , Pspice Evaluation v6.3 $\odot$ , and Micro-Cap V v2.0 $\odot$ .

The simulations in this book were computed using three PC desktop computers. The computers utilized 133 Mhz Intel® Microprocessors, 48 Meg RAM, and Windows NT 4.0 @. The computers were connected to a

#### Introduction

local network of six computers. The run times of the circuits are dependant on the capabilities of the computers running them as well as the .OPTIONS statements in the simulation. This being said, the simulation times noted after the simulations are **reasonably** accurate. Don't expect your computer will run at these times. Any simulation software can be made to run faster or slower than any other software! Just by changing the .OPTIONS statements, simulations have been shown to run 14 times faster [Sandler, 1996]. Each circuit can be optimized for speed differently. Tricks that speed up simulations in one circuit may not work in another, or even have the opposite effect on speed. SPICE simulations are a trade off between simulation speed, accuracy, and convergence [Kielkowski, 1994]. We have made a reasonable effort to make an apples to apples comparison between the simulation speeds of the software in this book. The reader will notice that it is not predictable which software package will run the fastest on any single circuit. The real purpose of including the run times is to provide the user with a guess as to how long the circuit will take to simulate on their own computer, nothing more.

The reader will also note that in some circumstances, one or more of the simulation software results will not match with the hardware results. We have attempted to explain the reasons for this in each of the circuits where this occurs. Bear in mind, SPICE is one of those tasks in life where you get out of it what you put into it. If you put very little effort into understanding what the model or circuit is doing, chances are your simulation accuracy will reflect that.

The CD ROM contains three folders, one for each of the three simulators. Each folder contains the .CIR files of that particular simulator. The circuit names are provided in the document for that circuit. For example, Circuit #1, a 4<sup>th</sup> Order Butterworth Low Pass Filter list the file names for that circuit as: lp\_fltr (Ispice), lpflt (Micro-Cap), lp\_flt (Pspice).

The schematics for most of the circuits contained in this book can be entered into the simulator in several minutes. The .CIR files can be cut and paste into the text editor and ran, or more importantly, the simulation control parameters can be viewed.

The options useful in helping to resolve non-convergence issues.

We have put a great deal of effort into the construction of this book. It is our sincere hope that the reader benefits from our hard work.

#### References

Kielkowski, Ron M. 1994. Inside Spice. New York: McGraw Hill.

Sandler, Steven M. SMPS simulation with SPICE. 1996. McGraw Hill.

Description of Ispice, Pspice, and Micro-Cap Simulators

2

Expedition<sup>™</sup> Series

quest a free CD tod

## Description of Ispice, Pspice, and **Micro-Cap Simulators**

The development of SPICE was instigated by Ron Rohrer, a junior faculty member at the University of California, Berkely. Rohrer was teaching a class on circuit simulation, in which he and Larry Nagel developed a simulator, in FORTRAN source code, that was to be named CANCER (Computer Analysis of Nonlinear Circuits Excluding Radiation). Due to the difficulties in testing circuits of the small sizes of IC's, SPICE was thought to be an answer to the quick and reliable design of integrated circuits. Larry Nagel increased the capabilities of CANCER by increasing the 400 component/or 100 node limit, adding new and improved components, and macromodels. In 1971, Nagel released this improved version of CANCER as SPICE1 (Simulation Program with Integrated Circuit Emphasis). In 1975 SPICE2 was released, which offered equation formulation for voltage defined elements as well as increased simulation speed. This was achieved through the developments of timestep control algorithms. Eventually, the capabilities of SPICE grew with the capabilities of computers. In 1983, SPICE2G.6 was released, which has become the cornerstone of many vendor-offered versions of SPICE compatible circuit simulation programs. SPICE2G.6 has been the industry standard for many years. Motivated by the increased use of UNIX workstations, SPICE2 was converted into C source code and released as SPICE3. Although SPICE3 is not backwards compatible with SPICE2, the new features far out weigh this drawback. SPICE3 has a technical advantage of being readily modified because it is written in modular C code. SPICE3 also offers more and improved device models and analysis. A major advantage is the addition of a graphical post processor, which graphically presents and facilitates waveform computation of simulation results. As SPICE3 provides more of the features offered in SPICE2G.6, it becomes a more viable replacement of SPICE2G.6. [Kielkowski]

Understanding the development of SPICE is useful in making a worthwhile comparison of vendor-offered simulation software. The foundation of many vender-offered simulators is Berkely SPICE3F.5. This is the simulator engine that dictates the algorithms used to generate a solution for a given simulation.

Three of these software manufacturers: Microsim (Pspice), Intusoft (IsSpice), and Micro-Cap V (Microcap) have their products featured in this book. These software manufacturers took the Berkley core program SPICE3F.5 and created a shell program around it. The shell creates the

http://www.pcbcafe.com/BOOKS/SpiceHandBook/03\_chapter02-01.php (1 of 3) [19/01/2002 22:00:44]

Description of Ispice, Pspice, and Micro-Cap Simulators

schematic using a sophisticated set of CAD tools. The shell then translates the schematic into the language of SPICE. The circuit is processed by SPICE and an answer is generated. The shell then takes the result from SPICE and passes it into a graphics post processor in order to view the answer in a meaningful form.

Because of this symbiotic relationship between the core SPICE program and the shell, each of the three programs have roughly the same structure. Four separate modules are utilized.

The first module is the **schematic capture** program. Originally, using SPICE meant translating a schematic by hand into the SPICE programming language for calculation. The schematic capture program allows the user to pull down parts from a menu, wire the components using a mouse, and click a button to start the simulation. The abilities of the schematic capture program are beginning to approach those of true CAD programs, indeed, Pspice offers a tool for routing printed circuit boards. The schematic building feel of the schematic capture programs helps the SPICE user to quickly translate their circuit ideas into a schematic compatible with SPICE.

A **text editor** is also included with the shell packages. The text editor is invaluable for viewing the text generated output files of SPICE as well as investigating syntax errors and other subtleties of the SPICE programming language. The text output of SPICE is in an excellent format for exporting to other useful engineering tools such as Excel or Mathcad.

The third module is the **simulator** itself. As stated earlier, each of these programs use the core code from Berkely to iterate solutions of the circuit using mesh equations.

The fourth module is the **graphics post processor**. This module has the feel of an oscilloscope, with the output of the SPICE program being translated into waveforms that fit the user's idea of how the circuit should behave. Many different mathematical operations can be performed on these waveforms, making the most use out of the results of SPICE.

| Schematic<br>Capture                                                                                                                                                                                                    | Text Editor                                                                                              | Simulator                                                                     | Graphical                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                         |                                                                                                          |                                                                               | Post Processor                                                                                                                                                     |

| Allows users to<br>quickly<br>generate SPICE<br>compatable<br>program<br>graphically<br>Allows for the<br>construction of<br>symbols used<br>for generating<br>new circuit<br>models for<br>components<br>and for IC's. | Examine output<br>files from SPICE<br>Examine SPICE<br>code generated<br>by Schematic<br>Capture program | Performs<br>numerical<br>iteration of<br>circuit to<br>determine<br>solutions | Converts output of<br>Simulator into more<br>meaningful graphs and<br>waveforms<br>Has the ability to<br>perform complex<br>numerical calculations<br>on waveforms |

Table 2-1: The four Modules and their functions

A difference between these simulators is how the user interfaces with the simulator engine, and the features offered by the other modules of the individual vendor program. A user can create libraries, but most of the time will depend on the libraries that are provided by a vendor. Description of Ispice, Pspice, and Micro-Cap Simulators

Libraries are a distinguishing characteristic of a simulator. Libraries may be included or libraries can be purchased that are compatible with the simulator. The libraries of each of the three simulators are unique to that particular simulator. However, in many cases a bulk of the models in the library have been provided by the component manufacturer. These models are available free over the internet. The library governs the accuracy of the simulation in which they are used. It is very important to test and qualify models in a library, rather than assuming that they are accurate. Just because a model is in a library does not mean that it provides correct results.

Each of the three simulators have a schematic editor program, which is used to enter the circuit into the simulator. Accessing the overall quality of a particular schematic editor comes down to preferences. Even though an assessment may be made by the number of keystrokes or clicks of the mouse required to enter a circuit, a users effectiveness is a function of familiarity and comfort. Maximizing the performance of a schematic editor is dependent on the user and is difficult to determine.

The same can be said when evaluating the performance of the post processor of a simulator. Familiarity governs the ability of a user to manipulate the output data into a desirable viewing form. All of the post processors perform similar features and therefore accessing the performance of a particular post processor is inherent to the preferences of the user.

Basic Overview of SPICE

Free Evaluation

Expedition<sup>™</sup> Series

equest a free CD toda

## **Basic Overview of SPICE**

SPICE starts by making an initial guess at the circuits node voltages, and then using nodal equations of the circuit, calculates the mesh currents. The mesh currents are then used to recalculate the node voltages and the cycle begins. This iterative process continues until the nodal equations have been solved within specified limits. These limits can be set by using .OPTION parameters (Reltol, Vntol, and Abstol). As the difference between each iteration approaches zero, the simulation approaches convergence. SPICE uses the Newton-Raphson algorithm to solve the matrix of nodal equations if the circuit contains a nonlinear device. For a circuit containing only linear devices, SPICE use Gaussian elimination to solve the matrix.

SPICE Syntax and Tutorial

SPICE Syntax and Tutorial

The first line of any SPICE text program is the title of the program. This line is completely ignored by SPICE. The next few lines of code usually tell SPICE which analysis will be performed and what the bounds of that analysis will be. For example, we may be requesting a time domain analysis of a circuit (called a transient analysis). The information as to how long, what increments, and what section of the waveform is of interest is defined in this section of the code. Also defined here are global constants, subcircuits (models) used repeatedly in the main circuit, and instructions on which nodes are of interest in the final solution.

> \*EXAMPLE CIRCUIT #1 .TRAN 1U 100U 10U 2U UIC .OPTIONS METHOD=GEAR PRINT TRAN V(2) .IC V(7) = 12

#### Table 2-2: Typical lines of the beginning of a SPICE program

The middle section of the code defines the circuit itself. The structure of each component is roughly similar. The first variable is the reference designator. The next variables are the node numbers that the component is connected to. The remaining variables define the parameters of that component.

A simple example is a resistor:

R1 1 2 100K

In this line, a resistor with name R1 is defined, connected from node 1 to node 2 with a value of 100 Kohms. Several rules apply to defining components. The node number zero is reserved for ground. All circuits must have at least one ground connection. Also, reference designators are limited to alpha-numeric characters. Longer statements may be continued on the following line by using a + symbol as the first character to indicate a continuation from the previous line.

R1 1 0 100K

L1 1 2 10U

equest a free CD tod

SPICE Syntax and Tutorial

Q1 2 3 4 2N2222A

V\_INPUT 4 0 10

I\_OUT 3 0 PULSE 0 1 1U 100N 100N 10U 20U

#### Table 2-3: Typical lines of the middle of a SPICE program

The final line of any SPICE program must be the **.END** statement.

There are several basic analysis that are primarily used in the this book. An explanation of each is given in the following paragraphs. To modify the simulation controls in Micro-Cap V simply select the options button on the tool bar and select global settings. In Pspice click on the analysis button on the tool bar, select set up, and then choose options. In Ispice Click on the file button on the tool bar, select edit controls, at this point you can write your own .OPTIONS statement, or select the help button in the edit controls box and then click on options for help in selecting a .OPTIONS statement.

#### **DC Analysis**

Before SPICE performs any specified simulation, a DC operating point analysis, .OP, is performed. This establishes the DC bias point of the circuit. There must be convergence of this simulation before any other specified simulation can be performed. SPICE calculates the DC operating point by replacing all of the inductors with shorts, and all of the capacitors are open circuit. SPICE must determine the DC operating point within a specified number of iterations, otherwise a nonconvergence warning is generated, and the simulation is aborted. The default .OPTIONS statement used to determine the DC iteration limit is:

.OPTIONS ITL1=100

For nonconvergence, the value of ITL1 should be increased to greater than 500, which increases the maximum allowed number of iterations to determine the solution.

A . NODESET statement can also be used to reduce the number of iterations required for convergence. The DC voltage of a node can be specified by the user, and will be used by SPICE in the initial guess of the simulation. This can greatly reduce the number of iterations that are required for convergence.

If convergence is not attained through the use of a nodeset and increasing the ITL1 statement, then an ITL6 statement can be used. By setting ITL6=100, or any non-zero value, a source stepping algorithm is used, which decrements the voltages sources down to zero, or until convergence is reached and then they are stepped back up to their assigned voltage level. This appears to be the solution to all DC bias point convergence problems. However, there are bugs associated with the ITL6 function and should be used only as a last resort.

If the circuit contains semiconductor devices, then the circuit contains regions of zero conductance. This can result in a divide by zero error. To eliminate this problem, every PN junction in every SPICE semiconductor device has a GMIN transconductance in parallel with every PN junction. GMIN is assigned globally and has a default value of 100pmhos. The larger the value of GMIN, the faster the Newton-Raphson algorithm will converge to a solution. Raising GMIN decreases the size of the shunt resistor. The accuracy of the simulation is not effected as along as the current generated in the shunt resistors are lower than the relative error tolerance current resolution. [Kielkowski] A suggested value for setting GMIN is given in the following statement:

.OPTIONS GMIN=1n or 1u

#### **Transient Analysis**

A transient time domain analysis begins with a DC operating point analysis. SPICE calculates the DC operating point by replacing all of the inductors with shorts, and all of the capacitors are open circuit. SPICE must determine the DC operating point within a specified number of iterations, otherwise a nonconvergence warning is generated, and the simulation is aborted. The solution to the DC operating point determines the node voltages at the time T=0. SPICE then assigns the instantaneous I-V relationship of inductors or capacitors and uses a numeric integration routine to create and equivalent nodal matrix. The nodal matrix changes for every time step in the transient analysis. Each following Newton-Raphson iteration starts with an initial guess consisting of the previous set of node voltages. This expedites the iterative process, which continues until the solution is found or the maximum allowed iterations is exceeded. The maximum number of iterations is determined by the setting .OPTIONS statement ITL4. The default .OPTIONS statement is given below:

#### .OPTIONS ITL4=10

When the simulation steps to the next point in time, the transient solver determines the operating point at that moment in time. If the simulation does not reach convergence at this point in time, then the time step is reduced by one eighth. This is repeated until convergence is achieved or the maximum number of times that the time step can be reduced, which is specified by ITL4 is reached. A large time step, which is also user defined, in a transient simulation can result in convergence difficulties. This is particularly true for switching circuits. The time step must be small enough to provide enough resolution to identify switching voltage levels. Large voltage transitions, or device model discontinuities must be taken into account when assigning the transient simulation parameters. An Example of a transient simulation statement is given below:

.Tran Tstep Tstop Tstop Tmax UIC

.Tran 10u 10m 0 20u UIC

The Time step Tstep= 10u determines each point in time starting from zero that the transient solver will calculate a solution. A safe estimation of the time step is an order of magnitude less than the period of a switching waveform. For example, when selecting the time step for a 100KHz oscillator (period=10usec), the time step should be approximately 1usec. Tmax, the maximum time step can be left out (at default), or specified to increase (decrease TMAX), or decrease (increase TMAX) simulation accuracy. This allows the simulator to take larger steps when the voltage levels in the circuit experience little change. A transient time domain analysis can prove to be the most difficult to get to converge.

#### **AC Analysis**

An AC analysis begins by determining the DC bias point of the circuit.

http://www.pcbcafe.com/BOOKS/SpiceHandBook/03\_chapter02-03.php (3 of 4) [19/01/2002 22:00:52]

SPICE Syntax and Tutorial

This can be critical, because it determines the state of the active devices. For instance, the output of a linear regulator or operational amplifier is different if it is operating in the linear region, or if it is operating in the saturated region. After SPICE determines the DC operating point, the large signal transistor and diode models are converted into linear small signal models. All nonlinear effects of the circuit will not be accounted for in the AC frequency sweep, which generates a Bode plot/frequency response. Magnitude, phase, real, or imaginary data is produced.

1-888-44-WEB-44

Untitled

### **Convergence Problems**

Convergence problems can be the most perplexing aspect of performing a simulation. There is a methodology that comes with experience. This secton of the text will provide a structured attack that should cure most convergence problems. The convergence suggestions should be performed in the order that they are listed. They are prioritized manner that should be of the most benefit. Begin with the obvious.

#### **Common mistakes:**

- Verify that all circuit connections are valid, proper component polarity, and a DC path from every node to ground. RENET, or REDRAW.

- Verify that all components have the correct values (i.e. MEG instead of M(milli) for 1E6). Components with no assigned value may be set to a default value determined by the simulator.

- Verify that all model parameters are realistic; especially if the model was created or altered by you.

- Verify that every node has two connections.

- Verify that voltage or current generators have the correct syntax and appropriate values.

- Use a series equivalent in place of capacitors or current sources that are placed in series.

- Verify that the letter zero was not used in place of zero (0).

- If B elements are used in the circuit, verify that division by zero cannot occur.

- Verify that dependant source gains are correct.

#### [Hymowitz]

#### **DC Convergence Solutions**

Free Evaluation CD Expedition<sup>™</sup> Series request a free CD today

#### 1. Set ITL1= 400 in the . OPTIONS statement.

This setting increases the number of iterations that SPICE will perform before

generating a none convergence warning and aborting the simulation.

#### 2. Add .NODESETs.

Voltages can be assigned to the nodes of the top level schematic. The initial guess

made by SPICE to determine the DC bias point incorporates the nodsets. This can

greatly reduce the number of iterations required to converge, increasing the

probability of a simulation converging. Improper nodesets can result in inaccurate

results. Care should be taken in setting the .NODESET statements.

#### 3. Use pulse statements to turn on DC power supplies

Example: V1 3 0 5 DC

Becomes: V1 3 0 PULSE 0 15

This allows the user to turn on the power supplies. A rise time may also be used to

provide a realistic turn on.

#### 4. Set Gmin in the .OPTIONS statement.

Set GMIN=1n, or GMIN=1u. This sets the minimum conductance across all

semiconductor devices.

#### 5. Set RSHUNT in the .OPTIONS statement.

This option places a resistor, with the value assigned globally by RSHUNT, from  $% \left( {{\left[ {{{\rm{T}}_{\rm{T}}} \right]}_{\rm{T}}} \right)$

every node in the circuit to ground. A solution obtained using this convergence

technique could be made at an incorrect operating point. The solution should be

carefully examined.

#### 6. Set ILT6=100 in the .OPTIONS statement.

Source stepping decreases all of the DC stimulus until a DC bias point is

determined, or they are reduced to zero volts. The voltages are then gradually

http://www.pcbcafe.com/BOOKS/SpiceHandBook/03\_chapter02-05.php (2 of 5) [19/01/2002 22:01:01]

Untitled

stepped from the DC bias point that converged, which may be at ground, back to

the assigned value. The source stepping algorithm uses gradual increases in

voltage, to establish a new DC bias point, using the previous DC bias point as the

initial guess. This process continues until a DC bias point has been establish for

the assigned values of the stimulus of the circuit.

#### **Transient Convergence Solutions**

#### 1. Verify that DC convergence has been achieved.

View the error statements in the text editor to verify that that the convergence

problem pertains exclusively to the transient simulation.

## 2. Verify that the time step provides an appropriate resolution.

The time step must be small enough to provide appropriate resolution of the

switching waveforms generated by the simulation. The time step should be

assigned to an order of magnitude smaller than the shortest period in the

step should be set to 1uSec.

.TRAN 1u 3m

Other factors such as the on time or the duty cycle should be considered when

determine the time step. Once convergence has been achieved this value can be

maximized to reduce simulation time.

## 3. For oscillating or switching circuits, set METHOD=GEAR in the .OPTIONS statement.

This statement selects the type of integration method that SPICE uses to solve the

transient equations. Gear integration should be used for all switching circuitry.

Untitled

The default integration, trapezoidal, has a tendency to produce oscillations.

#### 4. Add UIC (Use Initial Conditions) to the .TRAN statement.

This statement causes SPICE to bypass the DC operating point analysis. Initial

conditions should be placed on capacitors at there expected operating voltage. Just

as with the use of nodesets, initial condition statements can produce incorrect  $% \left( {{{\left[ {{{c_{1}}} \right]}}} \right)$

solutions. Results should be verified for validity.

#### 5. Set ITL4=500 in the .OPTIONS statement.

This statement increases the number of iterations performed by SPICE, before a

nonconvergence warning is issued and the simulation is aborted.

#### 6. Set RELTOL=.01 in the .OPTIONS statement.

This statement decreases the accuracy of the simulation by increasing the relative

error tolerance required for convergence. This statement should not be set lower

than .01. The simulation run time is also reduced by increasing RELTOL. As a

general rule, every order of magnitude decrease of the relative tolerance results in

doubling the simulation run time.

#### 7. Reduce the rise and fall times of PULSE sources.

Drastic changes in voltage can result in nonconvergence problems. Soften the

edges of the pulse source by increasing the rise time and fall time of the pulse

waveform.

#### 8. Set TRTOL=40 in the .OPTIONS statement.

This statement is proportional to the step size used when performing a transient

simulation. The accuracy of the simulation can be compromised by changing the

TRTOL from the default of setting of TRTOL=7.

## 9. Reduce the accuracy of ABSTOL/VNTOL if current and/or voltage levels permit.

The default value of ABSTOL=1pA, and VNTOL=1uV, should be

set to about

eight orders of magnitude below the level of the maximum current and voltage.

#### $10. \quad \text{Set the RAMPTIME}{=} 10 \text{nS in the .OPTIONS statement.}$

This statement ramps all independent sources up from zero at the beginning of the

transient analysis. This statement is beneficial if the transient analysis will not

begin. Take care to allow enough time for sources to ramp up, otherwise this

statement could do more harm than good.

#### **AC Convergence Solutions**

#### 1. Do not use steps 3-5 of the DC convergence solutions.

Using these steps may not produce a valid DC operating point, which is essential for SPICE to linearize the circuit. See the AC analysis description. Once DC convergence is achieved, the AC analysis will also converge.

Convergence failures are not always a function of SPICE, and can not be fixed using .OPTIONS statements or other convergence techniques. Convergence failures may result from hardware problems.

#### References

Sandler, Steven M. SMPS simulation with SPICE. 1996. McGraw Hill.

Kielkowski, Ron. Inside SPICE. 1995. McGraw Hill.

Filter Circuits

Expedition<sup>™</sup> Series

# Filter Circuits

Filter circuits form the initial building block for many different circuits. Communications circuits require only certain frequency signals be passed onto transmitter and receiver circuits. Power converters use filters on the input bus to filter out spurious noise and on the output line to smooth the rectified signal. Digital logic circuits use bypass capacitors and RC networks to filter supply voltages that must travel some distance before reaching the IC. Delays required in some circuitry can be provided by filters. Filter circuits are so important to these and many other circuits because of the simple function they perform. Filters allow signals of desirable frequencies to pass, while blocking signals of undesirable frequencies. For most of the circuits, the transient response of the filter is matched to hardware results. For a select few filters a network analyzer was utilized to measure the response of the filter.

Although filters perform a simple function, the amount of circuits and design parameters used to design filters are much more complex. Filters can be optimized for a low Q in the pass band (Butterworth type) or a high attenuation in the stop band and steeper rolloff near the cutoff frequency (Chebyshev type). Filters that are used primarily for delays in circuitry might use the Bessel-Thomson type of filter. The large applications of the filter circuit equates to the equally large filter design types for the engineer.

Expedition<sup>™</sup> Series

quest a free CD tod

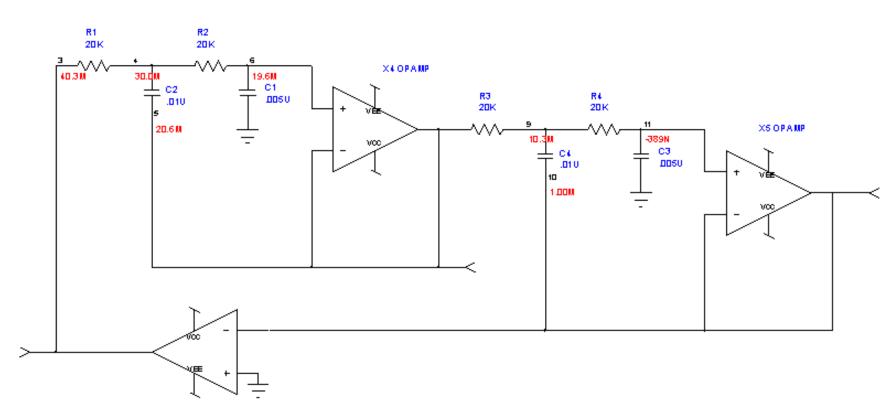

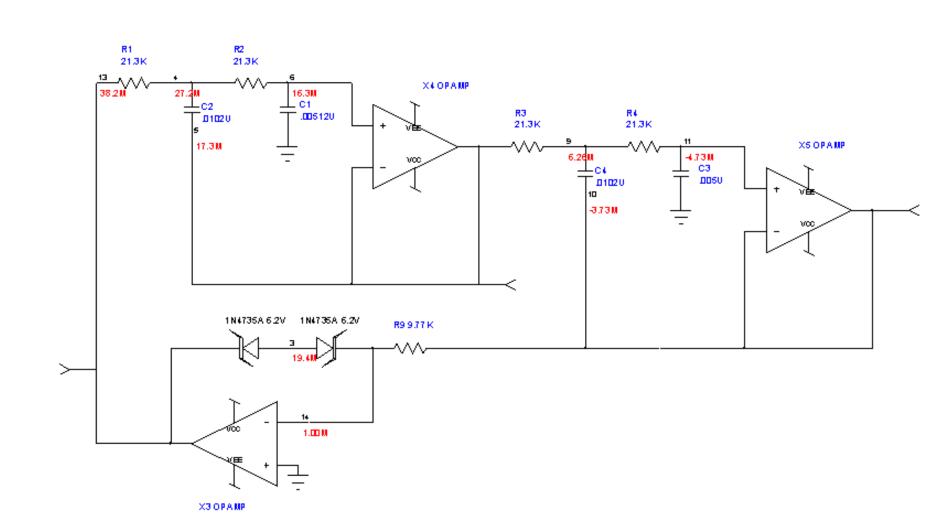

### #1: 4<sup>th</sup> order butterworth low pass filter

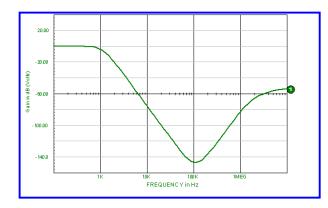

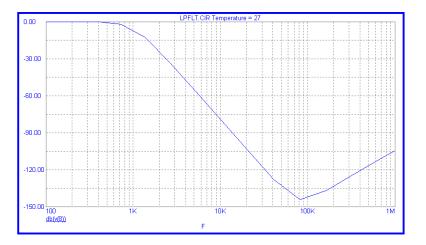

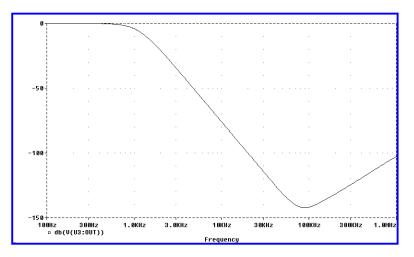

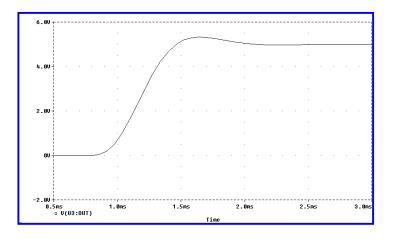

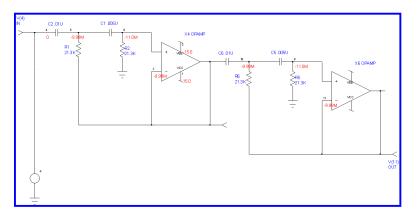

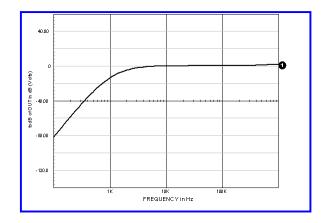

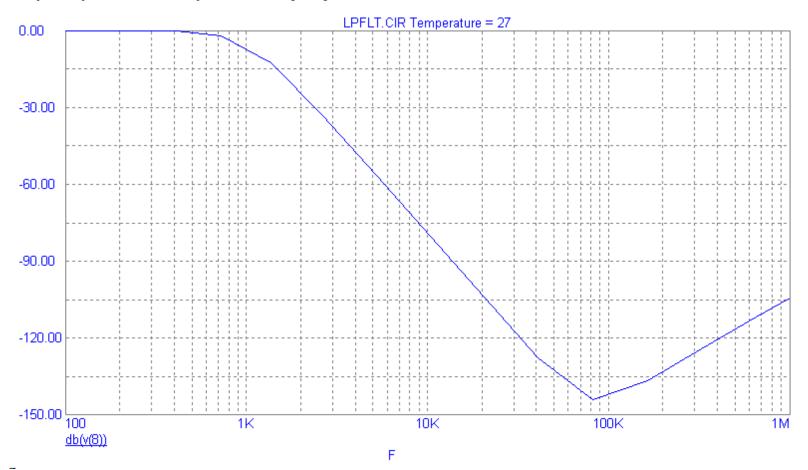

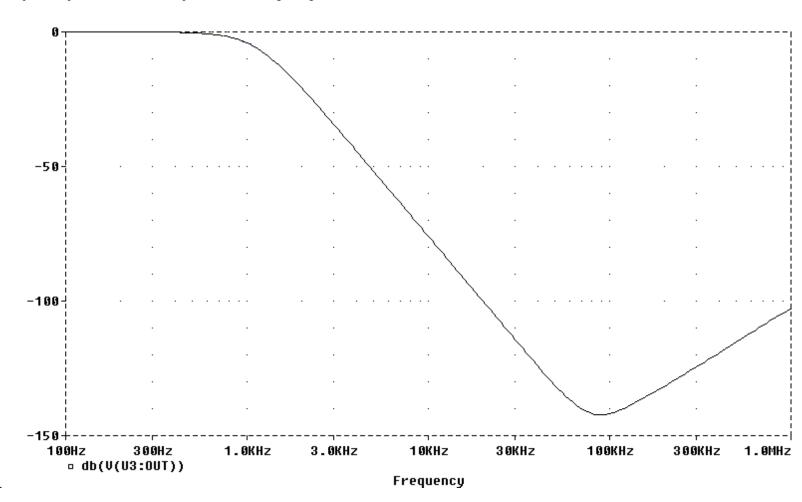

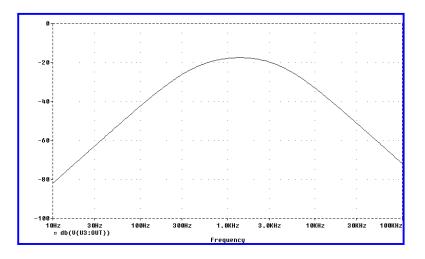

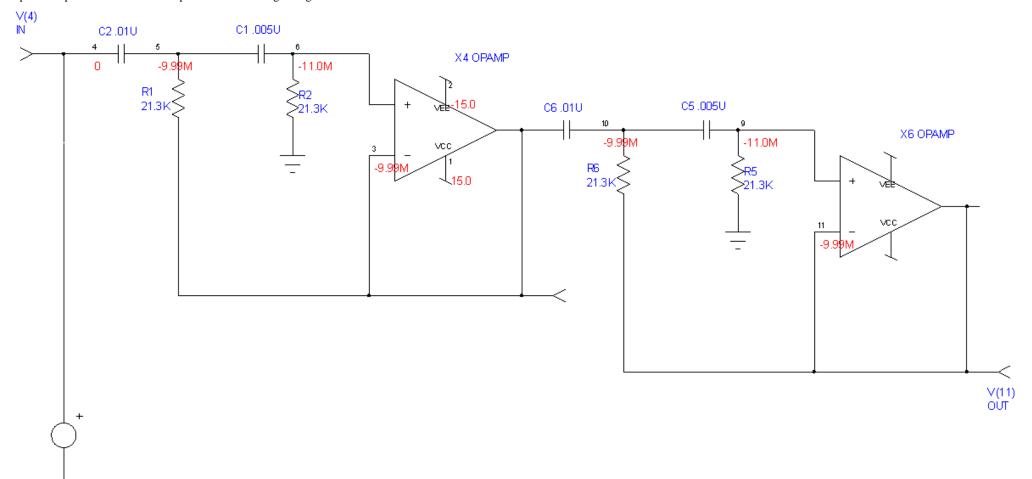

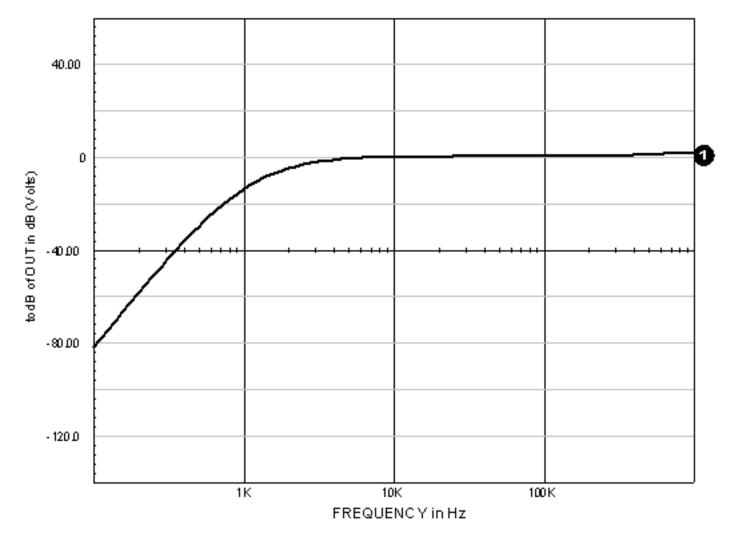

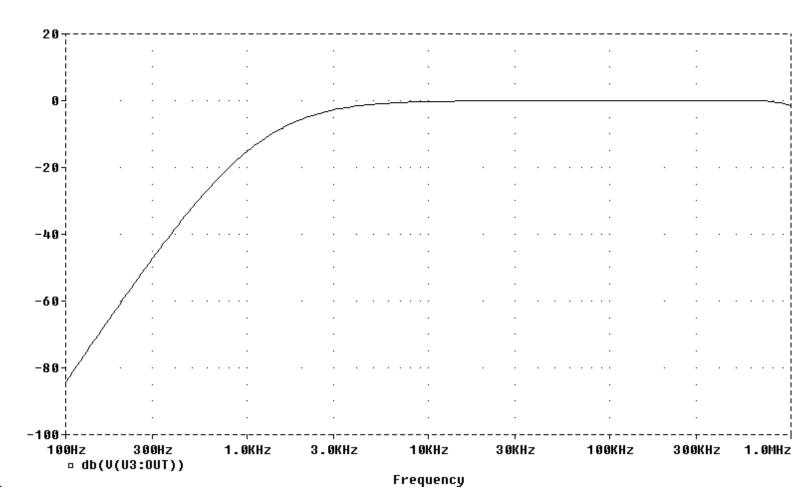

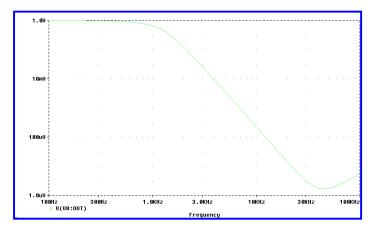

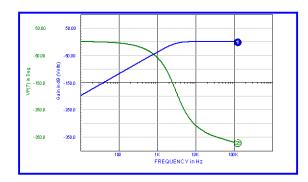

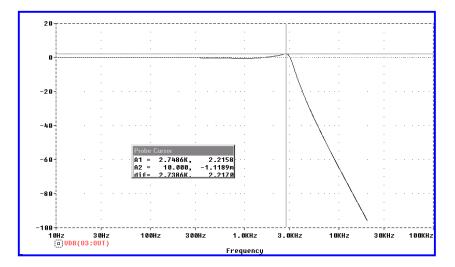

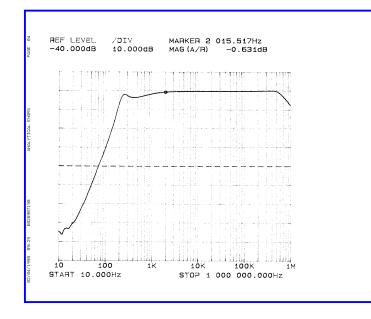

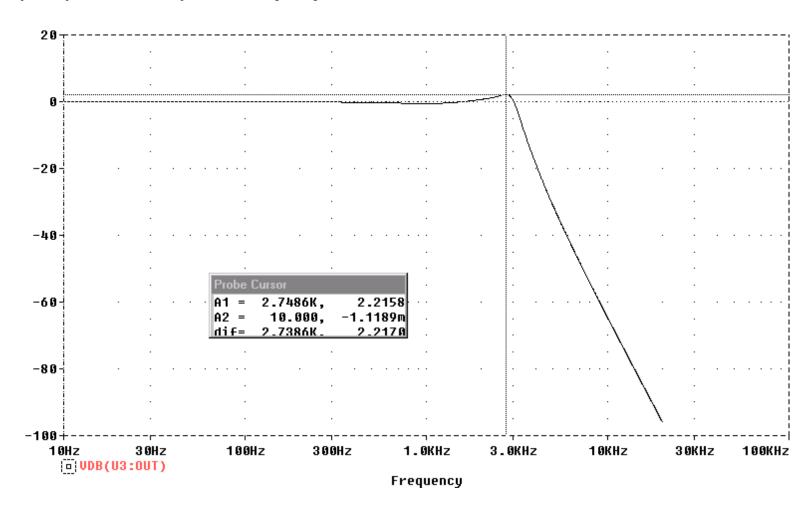

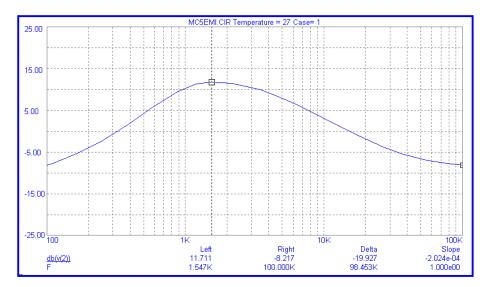

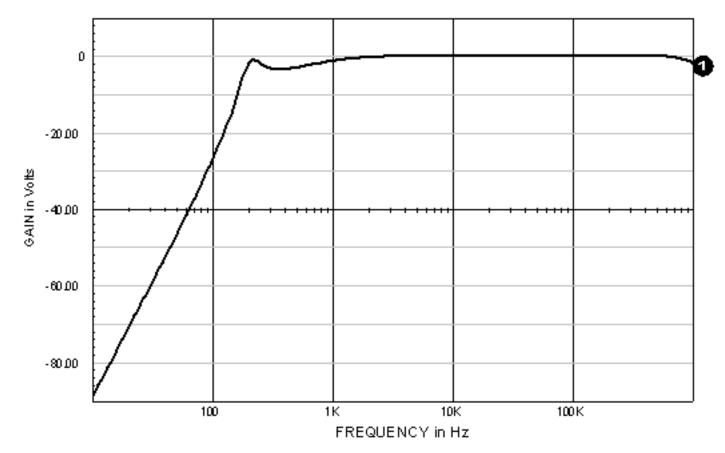

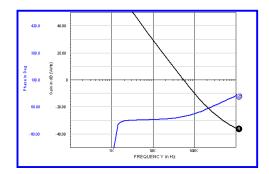

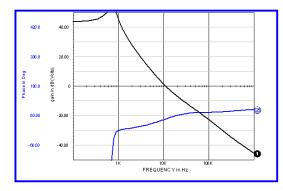

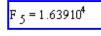

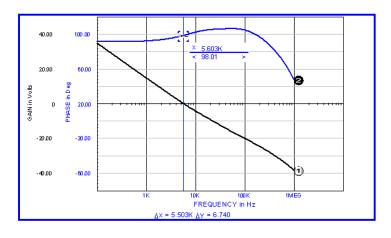

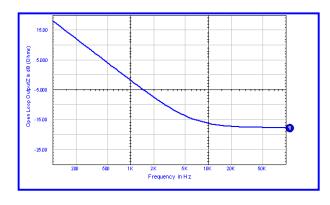

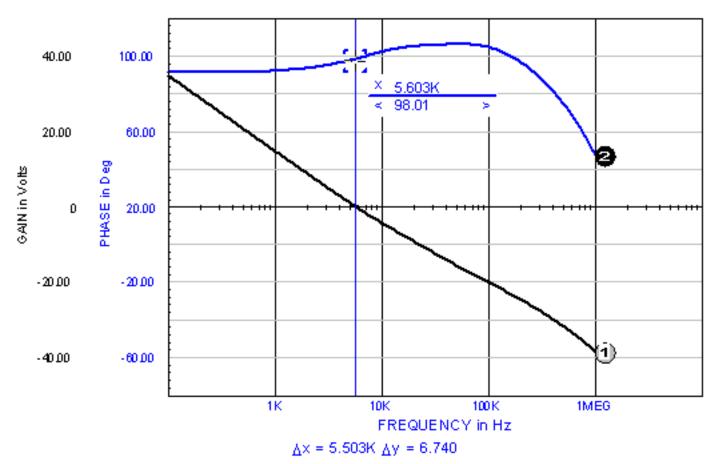

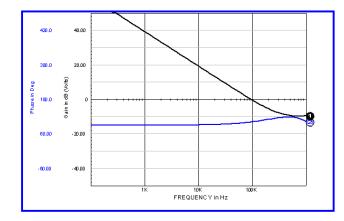

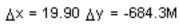

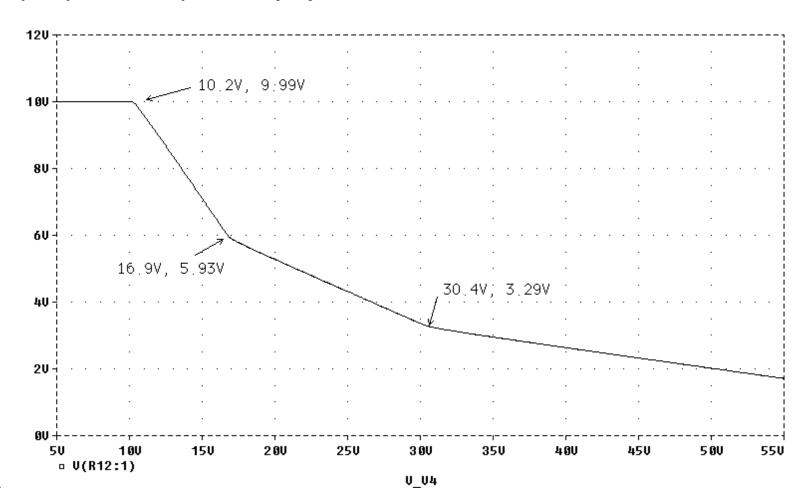

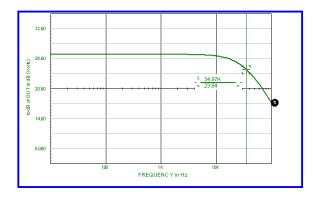

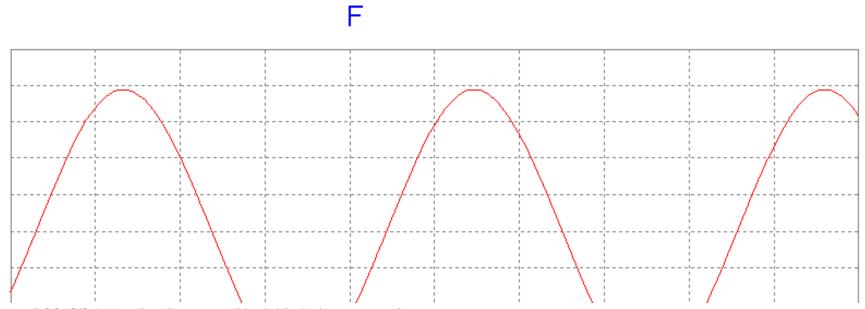

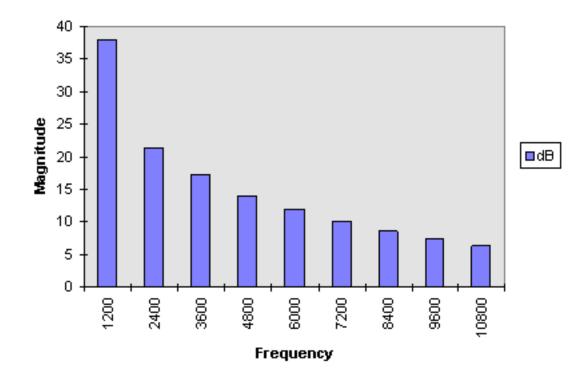

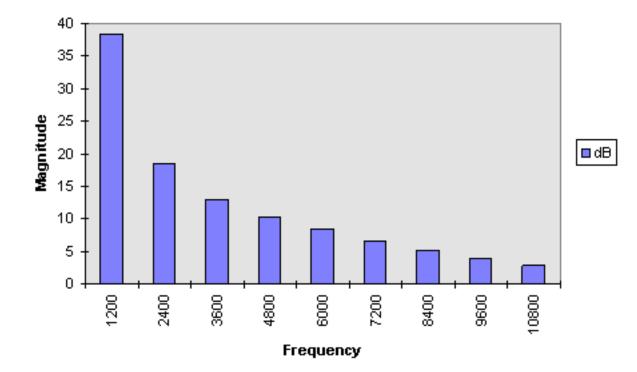

The first filter of the chapter is one of the most popular. The schematic of the  $4^{\text{th}}$  order butterworth response low pass filter is shown in Figure 1-1. The response of the filter to an AC sweep is shown in Figure 1-2. Notice the flat response in the pass band and the stop band frequency of 100 Khz.

#### Figure 1-1: Schematic of 4<sup>th</sup> order Butterworth low pass filter

Figure 1-2: AC filter response

Unfortunately, the lab used in the creation of the circuits in this book closely resembles the lab of other engineering companies around the world. We use 5% tolerance resistors and 10 % tolerance capacitors either soldered to a vector board or plugged into a solderless breadboard. This introduces various paracitics and inaccuracies to our result. In order to more capably show the use of SPICE simulation software, we will frequently run the simulations with the exact values of the resistors or capacitors being used in our lab breadboard. The measured resistors and capacitors of Figure 3-1 are shown in our breadboard configuration in Figure 1-3.

Figure 1-3: Breadboard configuration of 4<sup>th</sup> order Butterworth filter

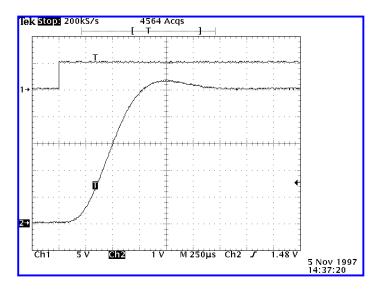

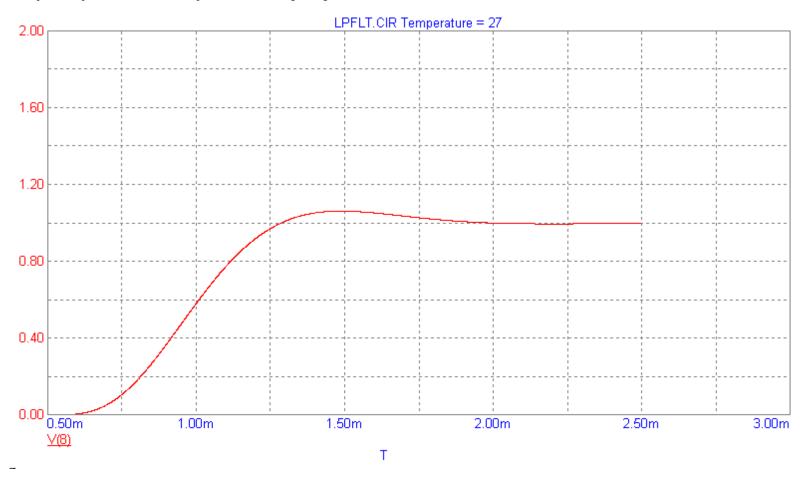

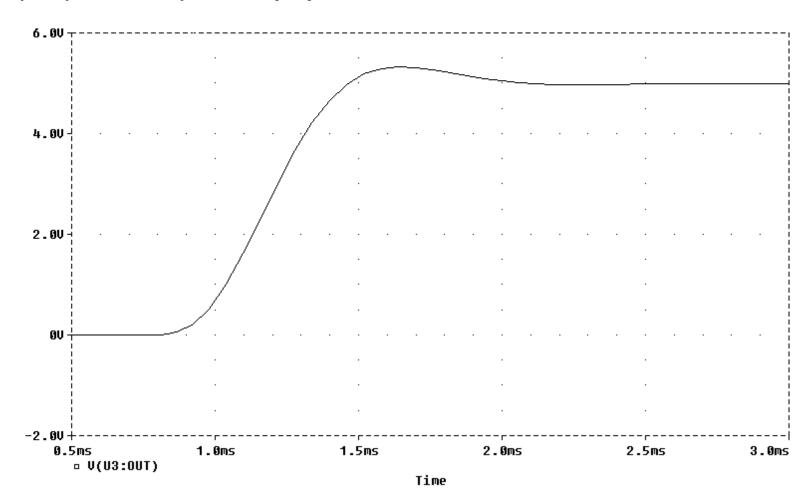

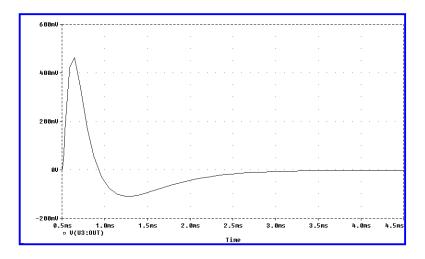

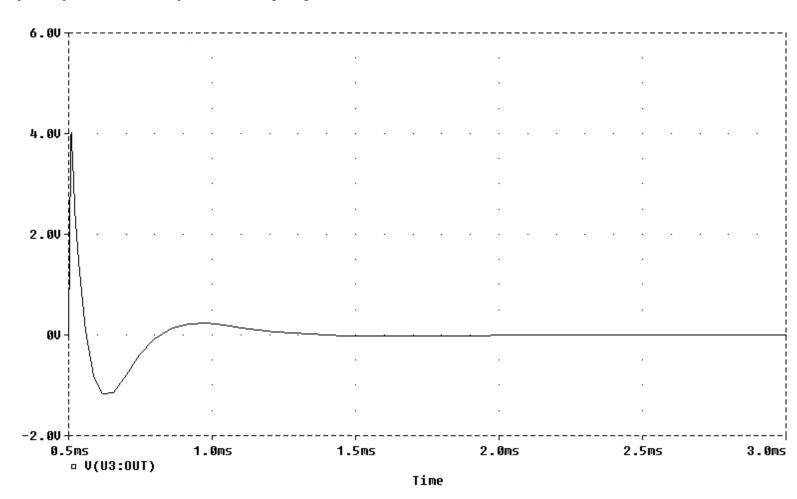

In order to correlate the breadboard to the SPICE circuit, a 5 volt pulse was applied with a 100 nSec rise time using the following command in a V source:

#### PULSE 0 5 750U .1U

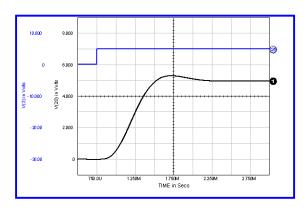

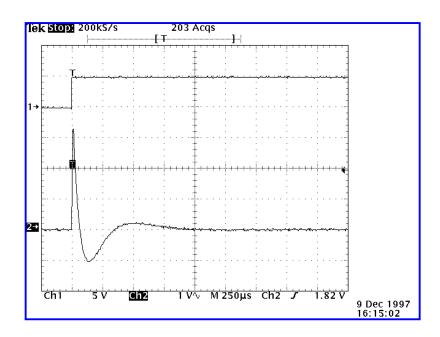

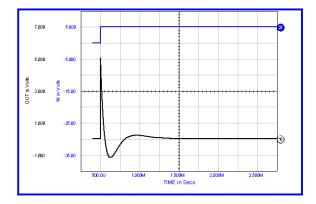

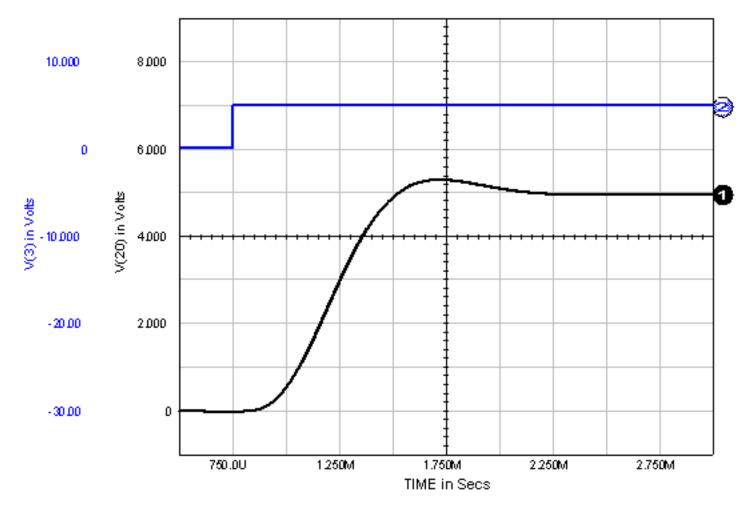

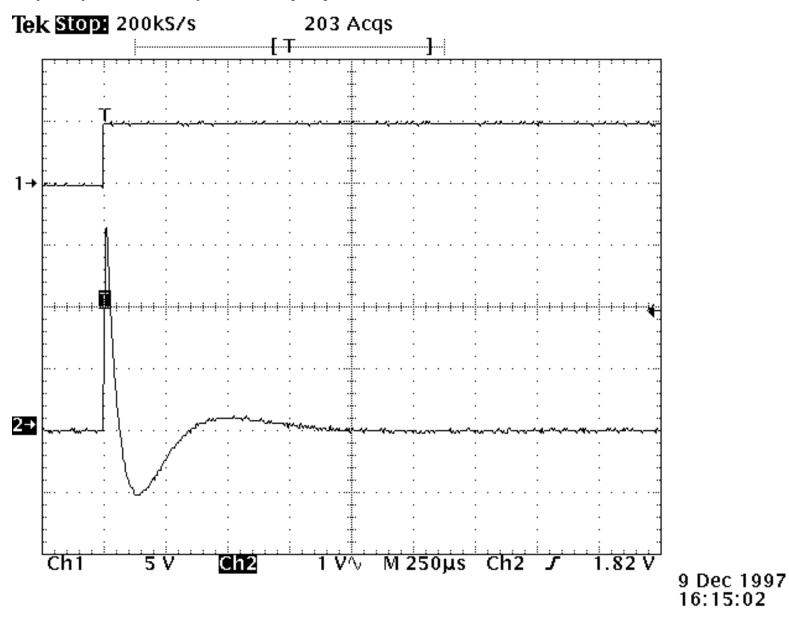

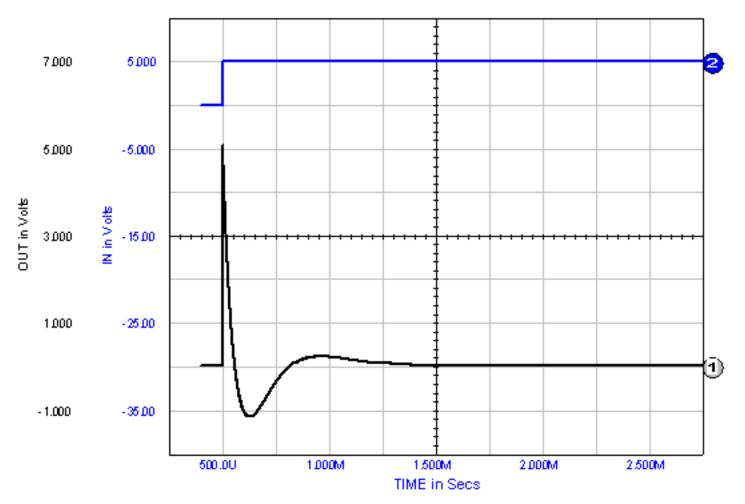

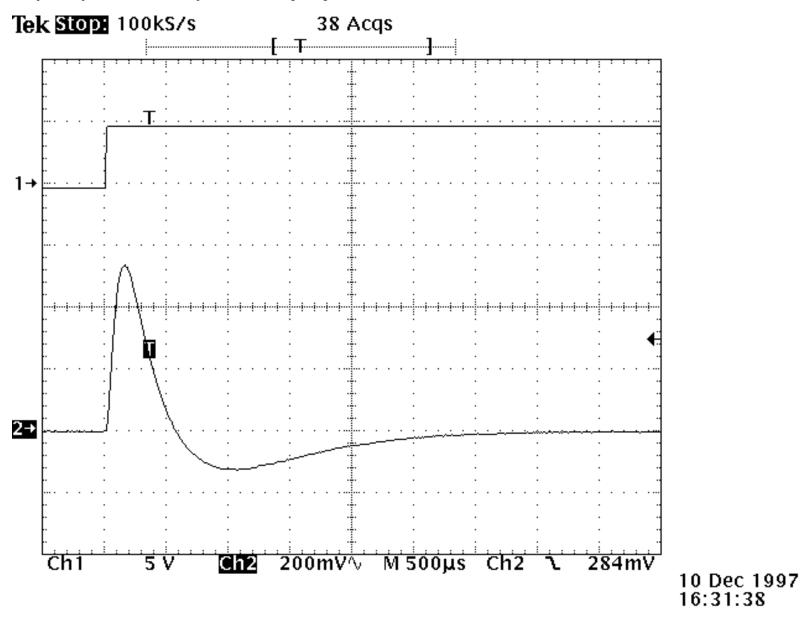

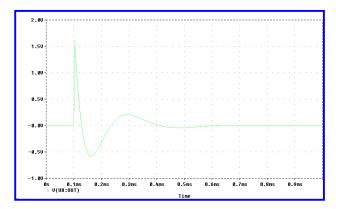

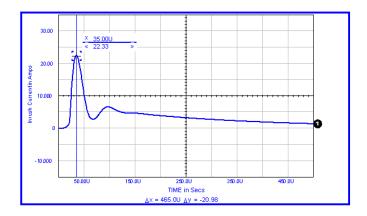

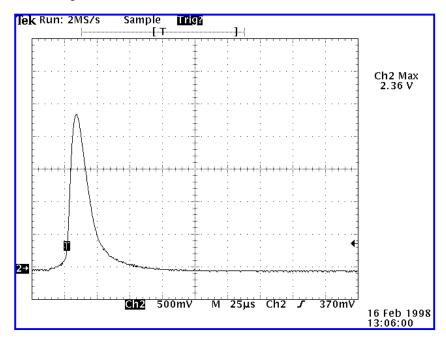

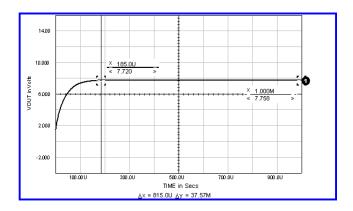

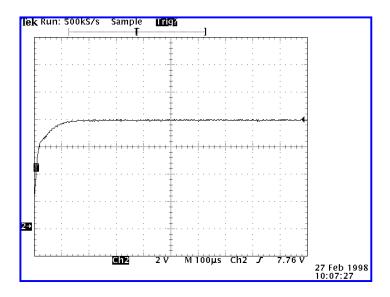

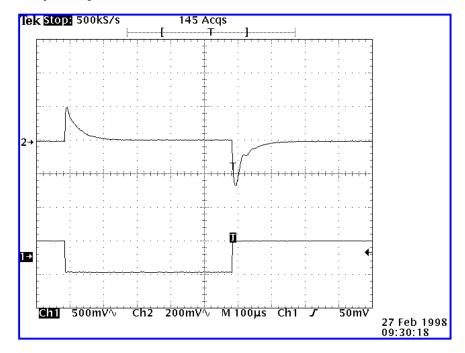

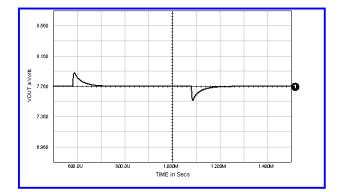

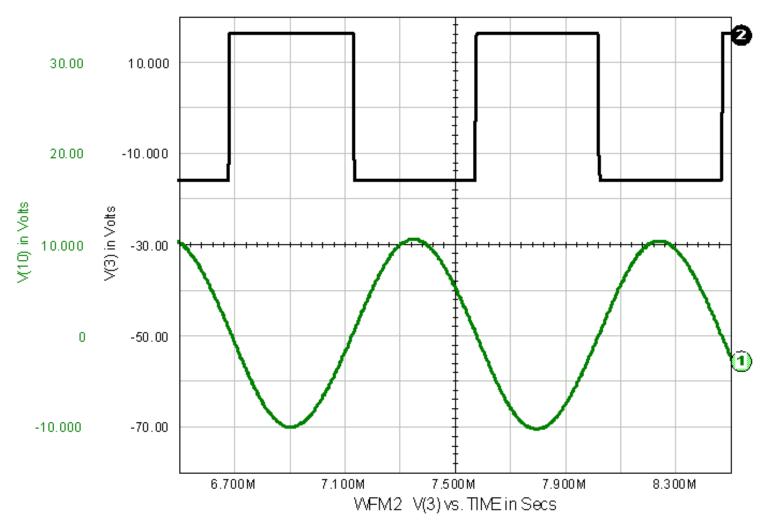

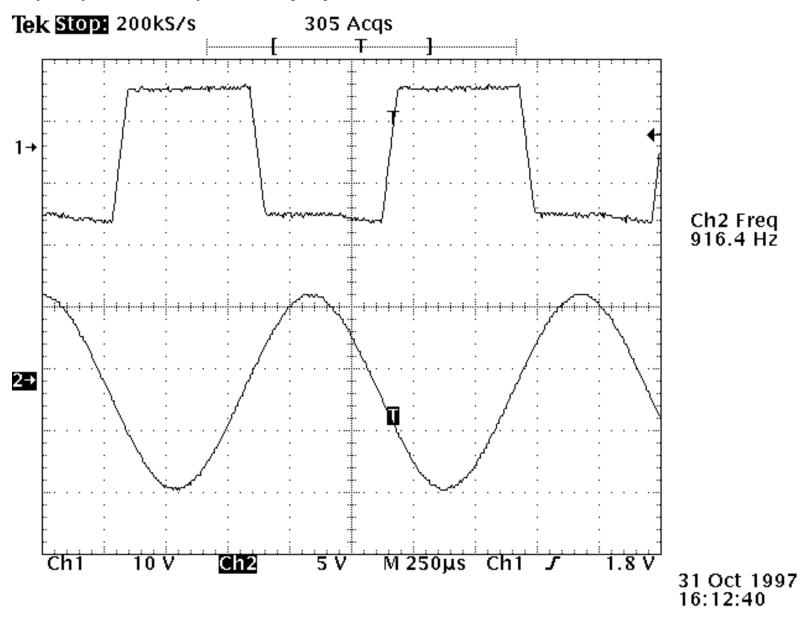

This creates a delay of 750 uSec to allow the filter to be at steady state when the pulse is applied. The step response of the breadboard circuit is shown in Figure 1-4A, while that of the IsSpice model is shown in Figure 1-4B. The top trace is the 5 volt pulse, while the bottom trace is the filter response measured at the output of the X5 Op-Amp.

Spice tip: Some convergence problems or problems in results are caused by attempting to run two different types of analyses in the same model at the same time. This phenomenon was noticed while simulating this circuit. If the AC simulation was performed at the same time in IsSpice, the operating point caused a convergence problem in the transient simulation. This can sometimes be remedied by manipulating .OPTIONS lines and adding IC (Initial Condition) statements to parts.

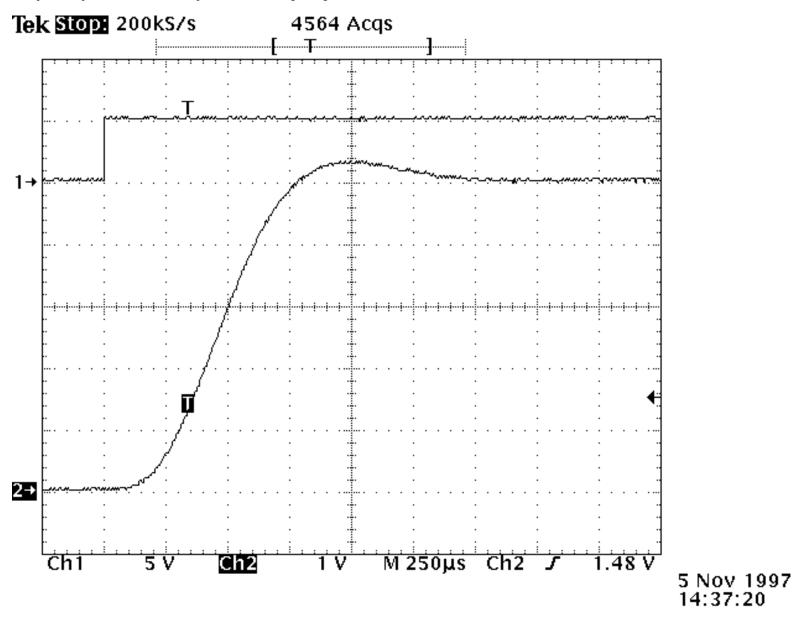

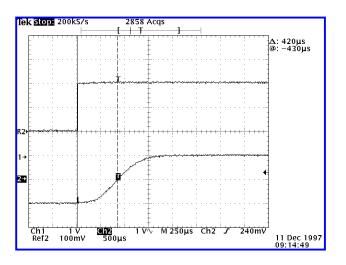

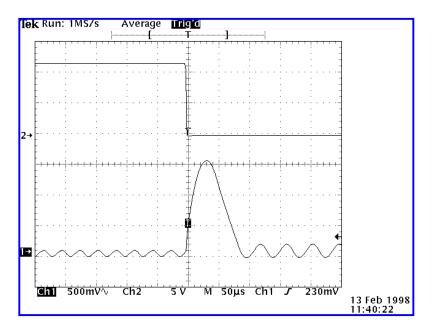

Figure 1-4A: Breadboard filter response to step input

Figure 1-4B: IsSpice filter response to step input

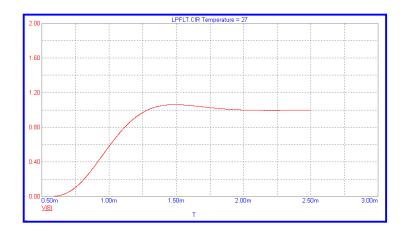

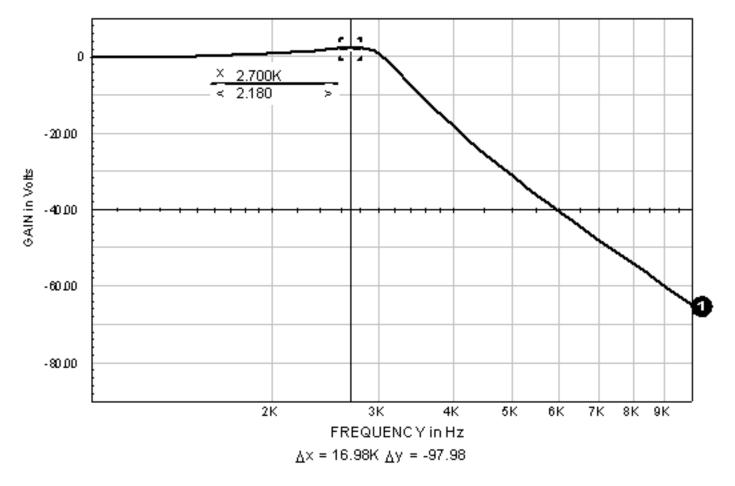

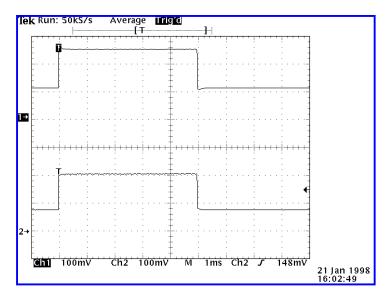

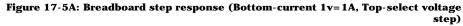

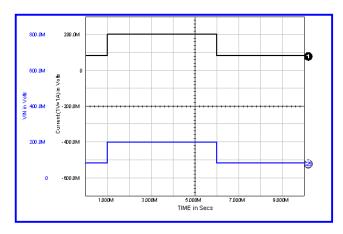

The circuit was also simulated on Microcap and Pspice. The Microcap results are

shown in Figure 1-5A and 1-5B, while the Pspice results are shown in Figure 1-6A and 1-6B.

Simulation tip: Notice in the results of the Microcap voltage step response simulation the magnitude of the output voltage was incorrect. The reason for this is unknown, however the lesson here is you must know the limitations of your models. Many times, these libraries can be provided by IC manufacturers or the software company. It is very important to remember that these models may not be accurate for the parameter that you are interested in. People make models to model different aspects of the part. For example, some models may have noise rejection modeled accurately, or AC characteristics, or input current draw, or some may not model any of these. If the model does not accurately reflect the characteristic you are interested in, this does not necessarily mean the model is useless or wrong (although this is a possibility).

Figure 1-5A: Microcap AC filter response

Figure 1-5A: Microcap filter response to step input

Figure 1-6A: Pspice AC filter response

Figure 1-6B: Pspice filter response to step input

| Run Time Summary                                                 |              |                |  |  |  |

|------------------------------------------------------------------|--------------|----------------|--|--|--|

| IsSpice v 7.6                                                    | PsPice v 6.3 | Micro-Cap V v2 |  |  |  |

| 17.016 Sec                                                       | 1.36 Sec     | 30.59 Sec      |  |  |  |

|                                                                  |              |                |  |  |  |

| Advantages: Moderate parts count, flat response in the pass band |              |                |  |  |  |

| Disadvantages: Filter Q greater than other filter types          |              |                |  |  |  |

Filenames: lp\_fltr (IsSpice) lpflt (Micro-cap) lp\_flt (Pspice)

order butterworth high pass filter

### **#2:** 4<sup>th</sup> order butterworth high pass filter

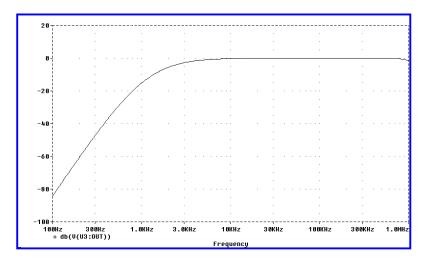

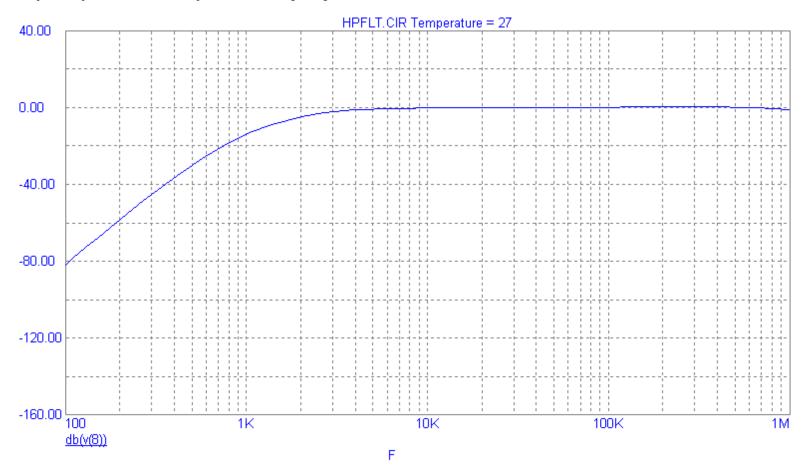

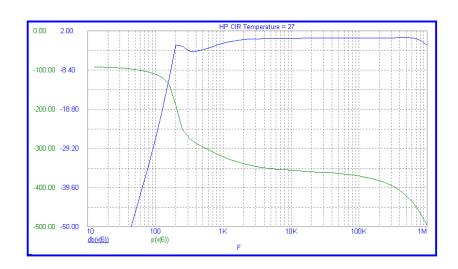

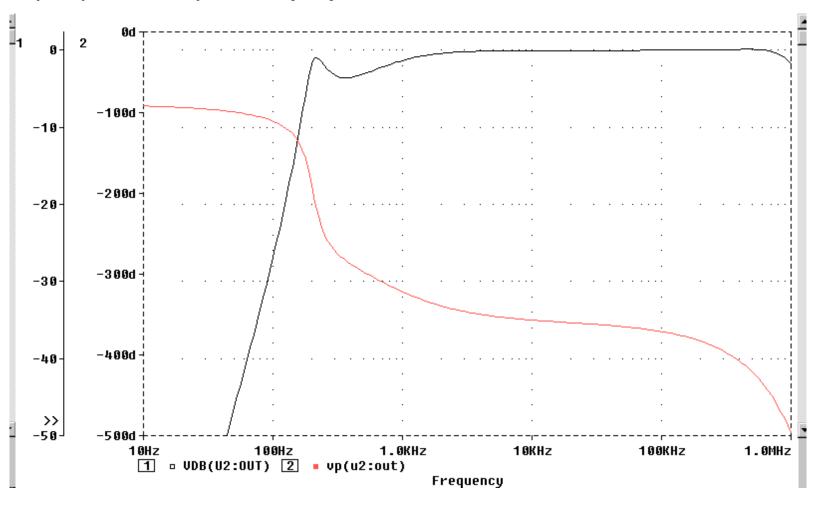

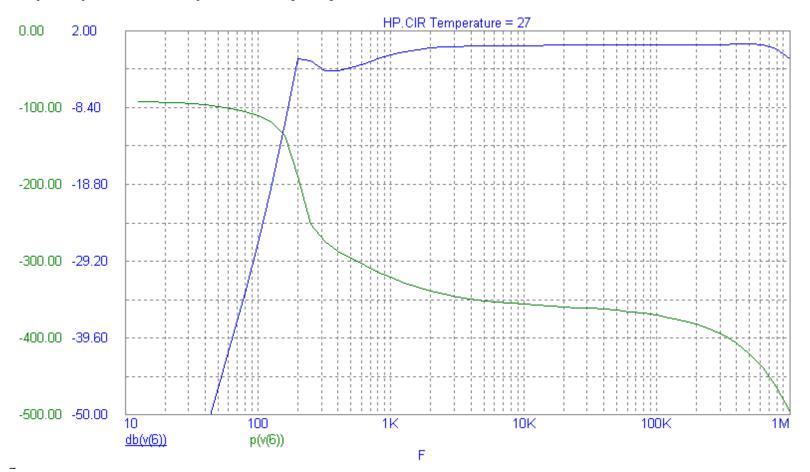

A quick modification to the circuit in figure 2-1 produces a high pass filter response. The schematic for the high pass filter is shown in figure 2-1 and the AC response of the filter is shown in figure 2-2.

Figure 2-1: Schematic of 4th order Butterworth high pass filter

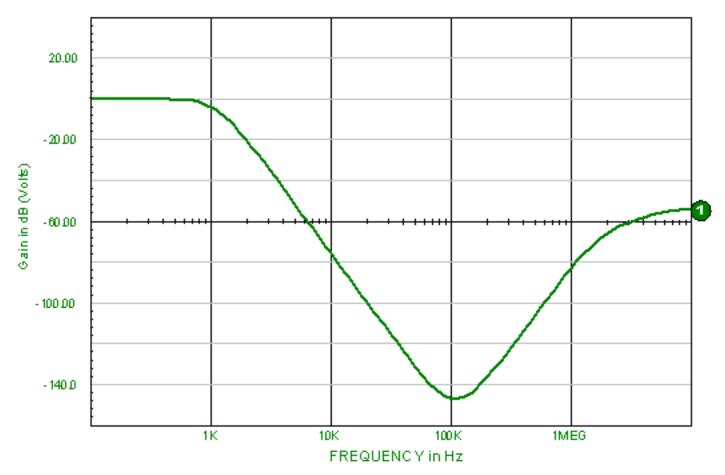

Figure 2-2: AC filter response

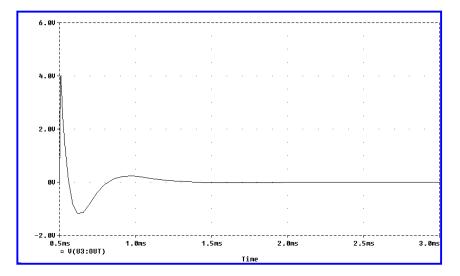

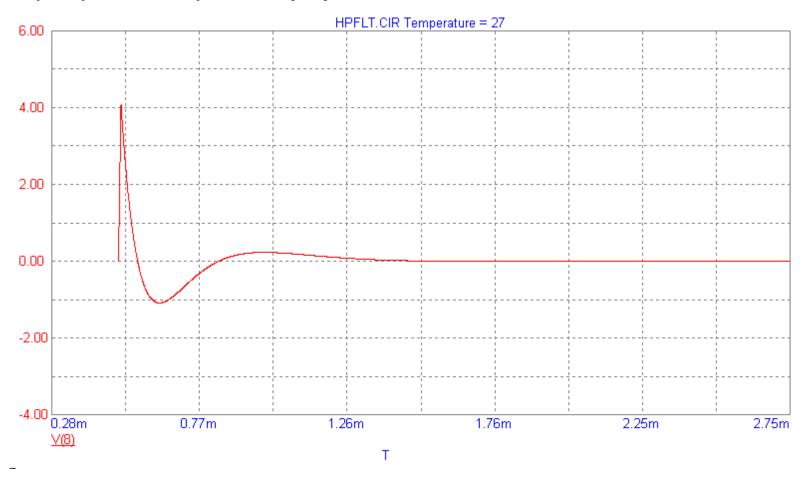

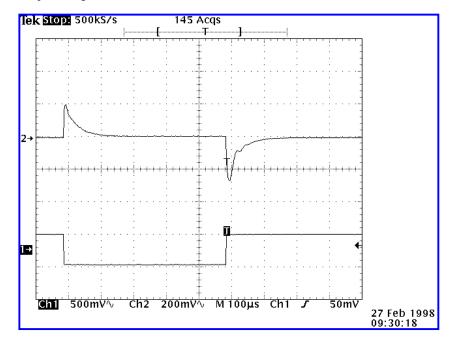

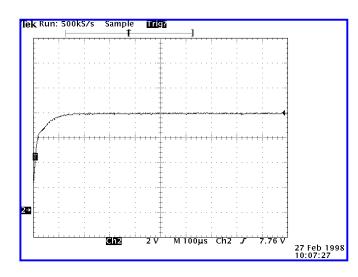

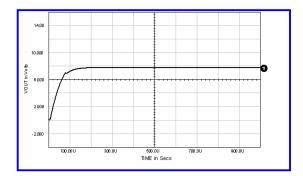

The same pulse in the low pass filter was applied to the high pass filter. The breadboard results are shown in figure 2-3. These may be compared to the IsSpice results shown in figure 2-4. The top trace is the 5 volt pulse, while the bottom trace is the filter response measured at the output of the X6 Op-Amp.

Figure 2-3: Breadboard filter response to step input

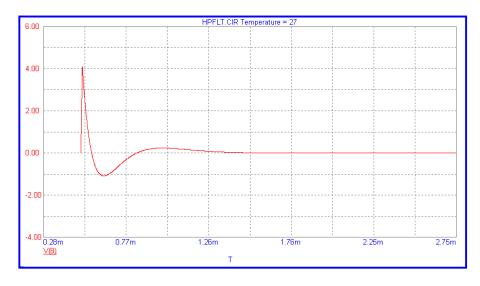

Figure 2-4: IsSpice filter response to step input

This circuit was also simulated using Microcap and Pspice. The results of these simulations are shown below.

Figure 2-5: Pspice AC filter response

Figure 2-6: Pspice filter response to step input

Figure 2-7: Microcap AC filter response

Figure 2-8: Microcap filter response to step input

http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-03.php (3 of 4) [19/01/2002 22:01:17]

| Run Time Summary                                                 |              |                |  |  |  |

|------------------------------------------------------------------|--------------|----------------|--|--|--|

| IsSpice v 7.6                                                    | PsPice v 6.3 | Micro-Cap V v2 |  |  |  |

| 21.566 Sec                                                       | 0.71 Sec     | 37.76 Sec      |  |  |  |

|                                                                  |              |                |  |  |  |

| Advantages: Moderate parts count, flat response in the pass band |              |                |  |  |  |

| Disadvantages: Filter Q greater than other filter types          |              |                |  |  |  |

Filenames: hp\_fltr (IsSpice) hpflt (Micro-cap) hp\_flt (Pspice)

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image746.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image747.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image749.gif

## http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image750.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image751.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image753.gif [19/01/2002 22:01:19]

order butterworth band pass filter

Expedition<sup>™</sup> Series

equest a free CD toda

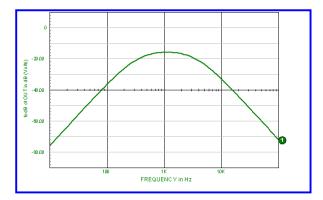

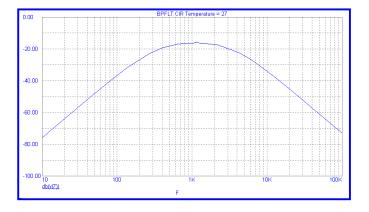

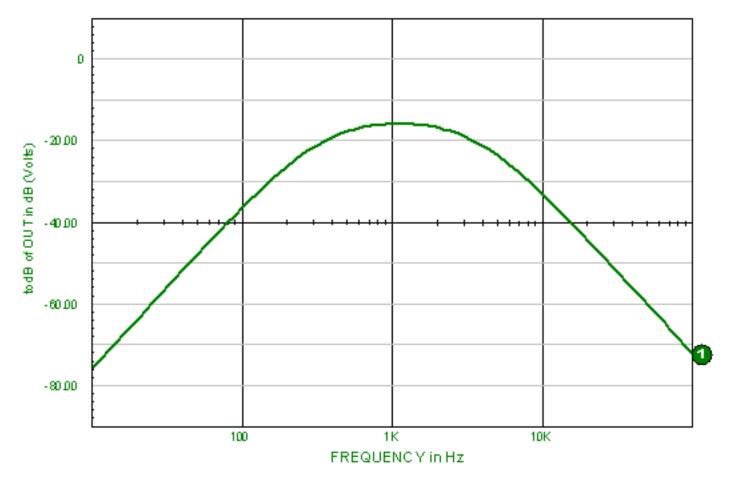

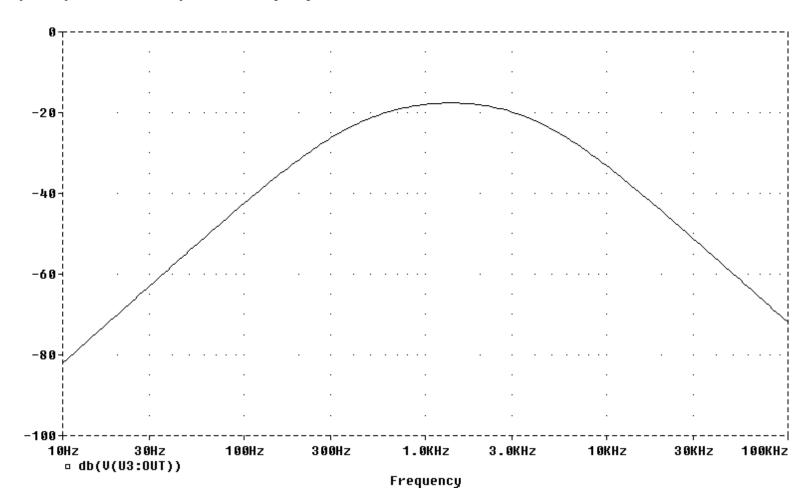

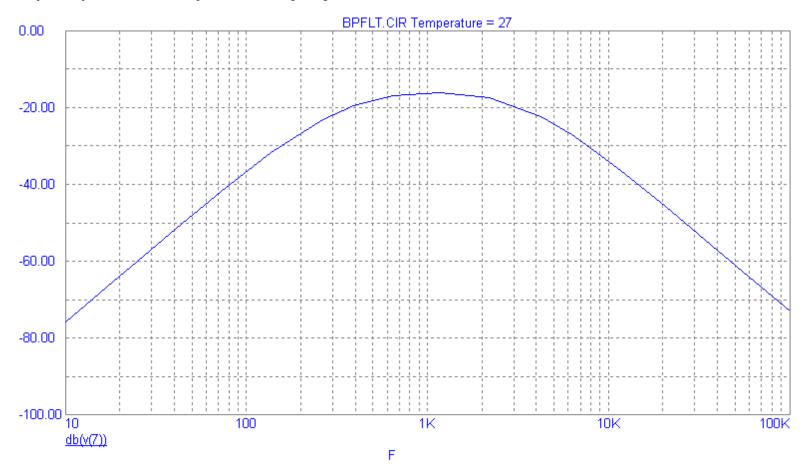

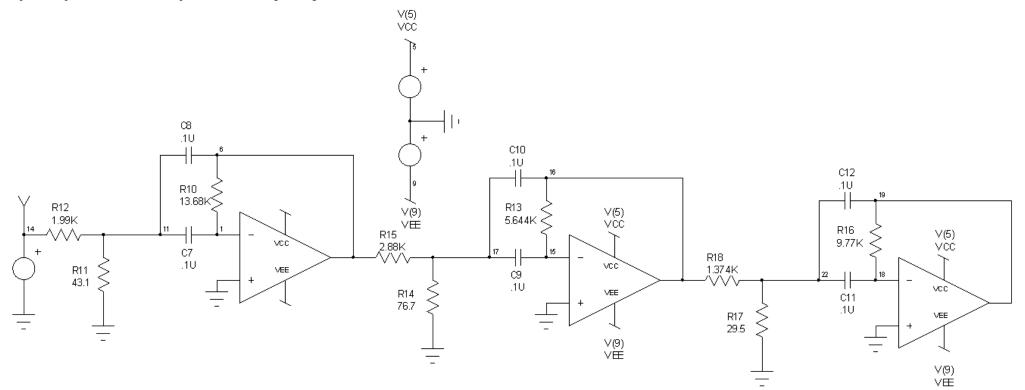

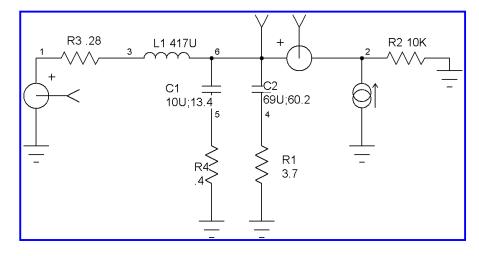

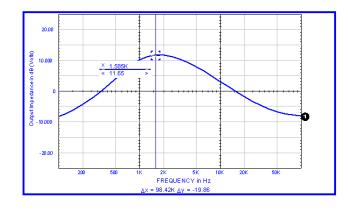

The schematic in Figure 3-1 shows the configuration for a butterworth band pass filter. The AC characteristic of the filter is shown in Figure 3-2.

Figure 3-1: Schematic of 4th order Butterworth band pass filter

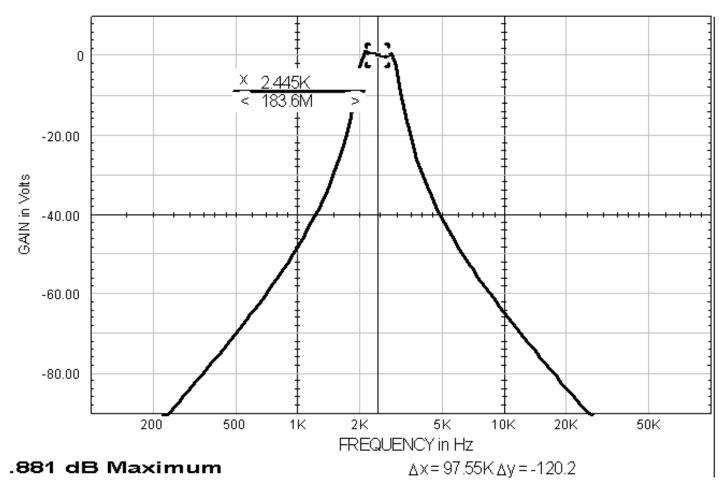

Figure 3-2: AC filter response

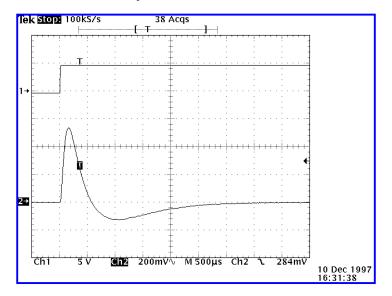

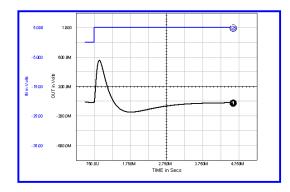

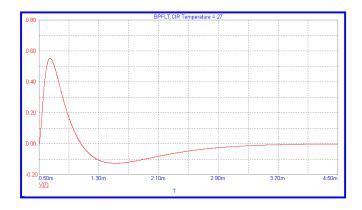

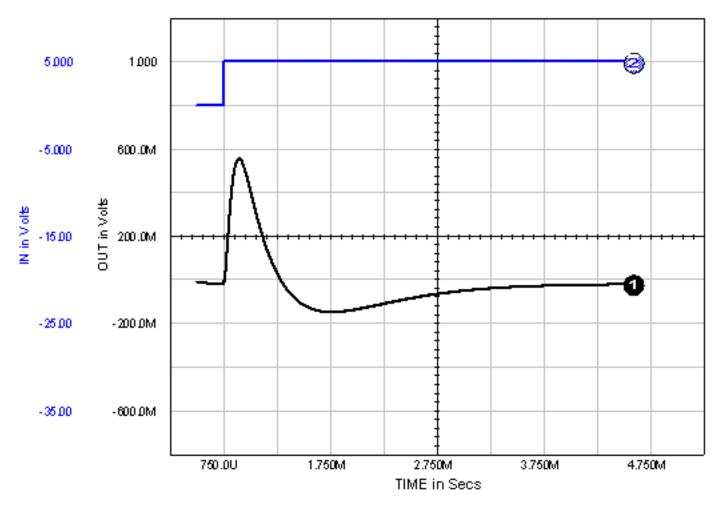

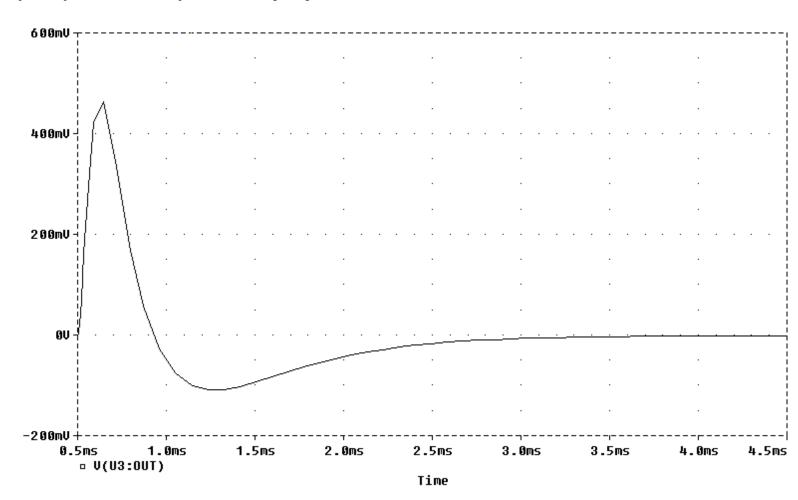

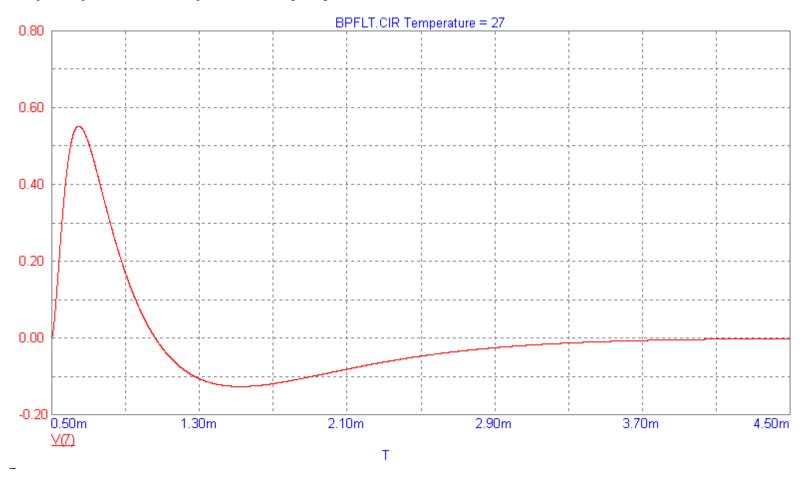

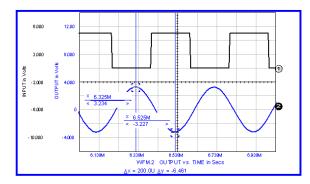

The breadboard circuit was pulsed with a 5 volt step. The results of the band pass filter to the input step are shown in Figure 3-3. The top trace is the input step and the bottom trace is the filter response at the output of X5. The IsSpice circuit response to the input step is shown in Figure 3-4.

order butterworth band pass filter

Figure 3-3: Breadboard filter response to step input

Figure 3-4: IsSpice filter response to step input

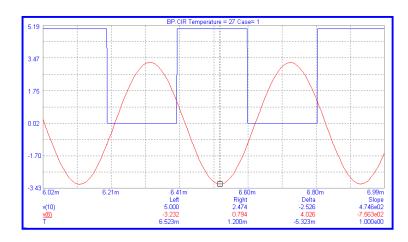

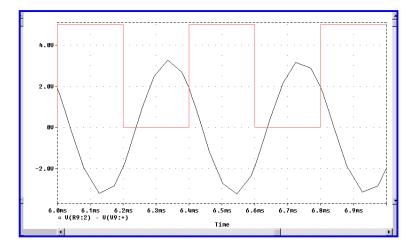

This circuit was also simulated using Pspice and Microcap. The results of these simulations are shown below.

Figure 3-5: Pspice AC filter response

Figure 3-6: Pspice filter response to step input

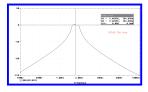

Figure 3-7: Microcap AC filter response

Figure 3-8: Microcap filter response to step input

**Run Time Summary**

order butterworth band pass filter

| IsSpice v 7.6                                           | PsPice v 6.3 | Micro-Cap V v2 |  |  |

|---------------------------------------------------------|--------------|----------------|--|--|

| 28.216 Sec                                              | 1.45 Sec     | 57.98 Sec      |  |  |

|                                                         |              |                |  |  |

| Advantages: Moderate parts count                        |              |                |  |  |

| Disadvantages: Filter Q greater than other filter types |              |                |  |  |

Filenames: bp\_flt (IsSpice) bpflt (Micro-cap) bp\_flt (Pspice)

Copyright 2002, PCBCafe. 1-888-44-WEB-44

\_

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image757.gif

## http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image760.gif

## http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image761.gif

Bessel-Thompson Delay low pass filter

# #4: Bessel-Thompson Delay low pass filter

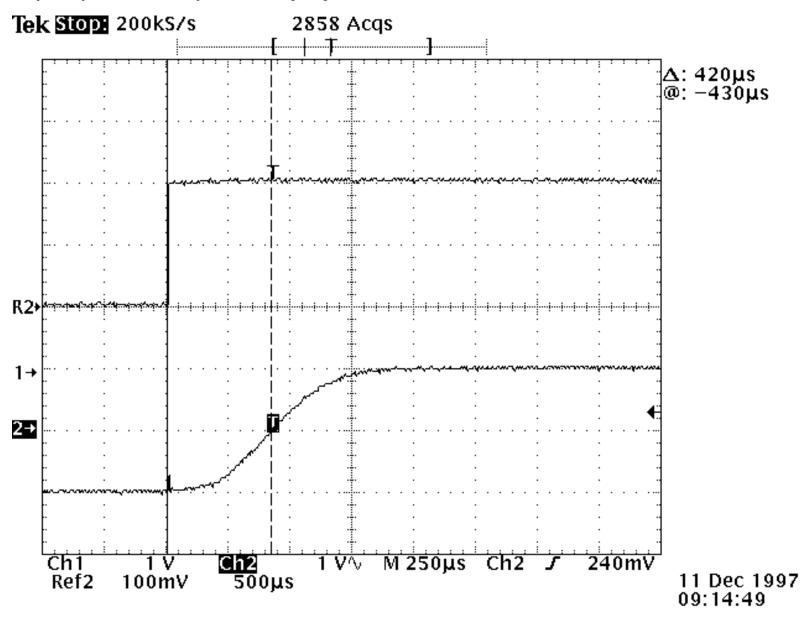

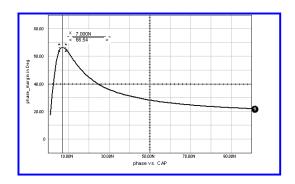

The primary purpose of this filter is to add a delay to a pulse or data sequence. The use of the RC time constant allows this delay to be added to both the rising and falling edge of the pulse. The ideal response of the filter is a perfect reproduction of the input delayed by a specified time constant. The time delay of the Bessel-Thompson is measured by the time the pulse occurs until the time the response is 50% of the input step height.

A Bessel-Thompson filter was designed to close to 500 us of delay. The design procedure followed gave exact values for all of the capacitors and resistors. These values are rounded to the nearest value of capacitor available. The three spice packages are used to determine what the implemented delay will be. Measured values of all the components used in the hardware are used. The schematic and the breadboard results are shown as figure 4-1 and figure 4-2 respectively.

Figure 4-1: Bessel-Thompson Delay filter

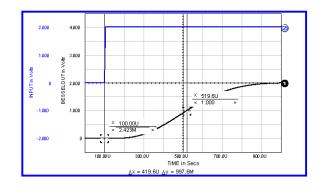

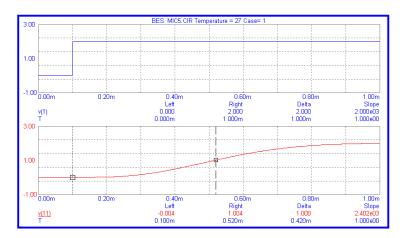

IsSpice had a built in LM124 model. The simulation response to a step input is

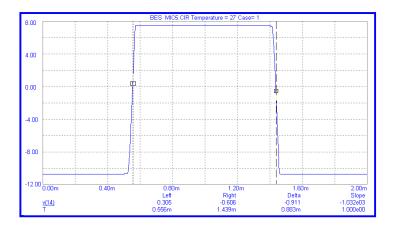

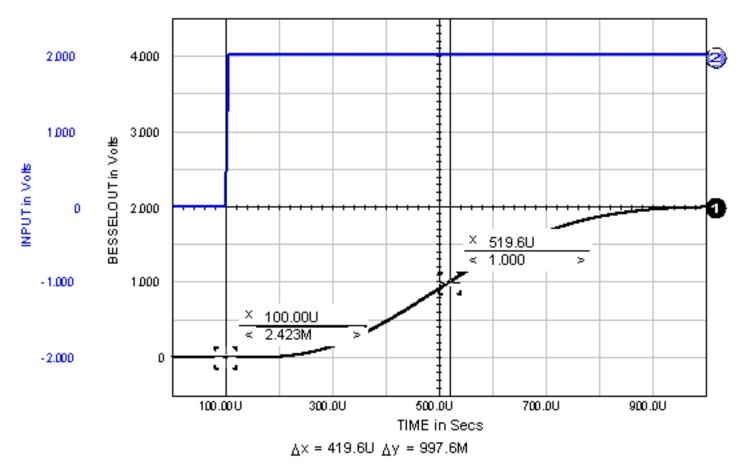

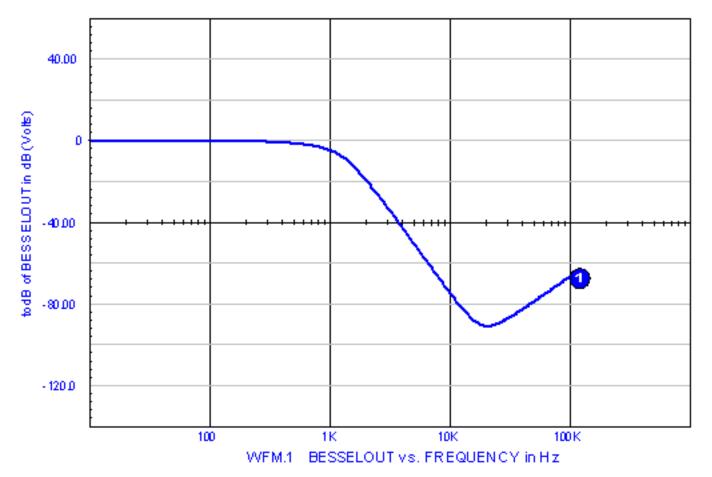

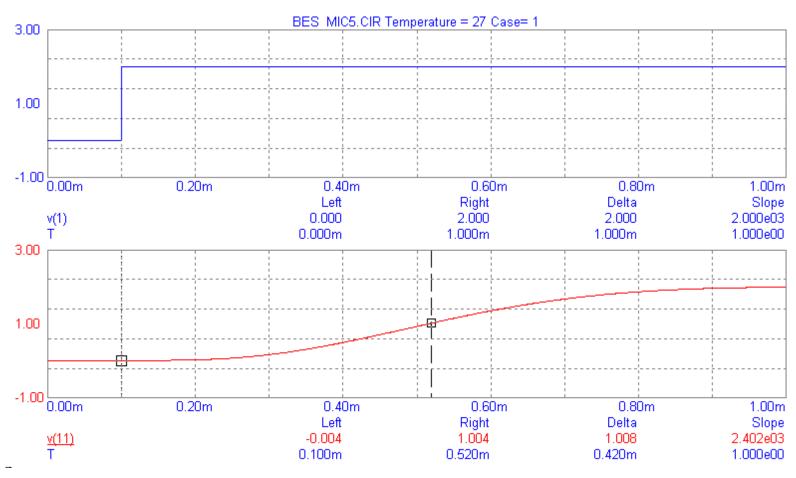

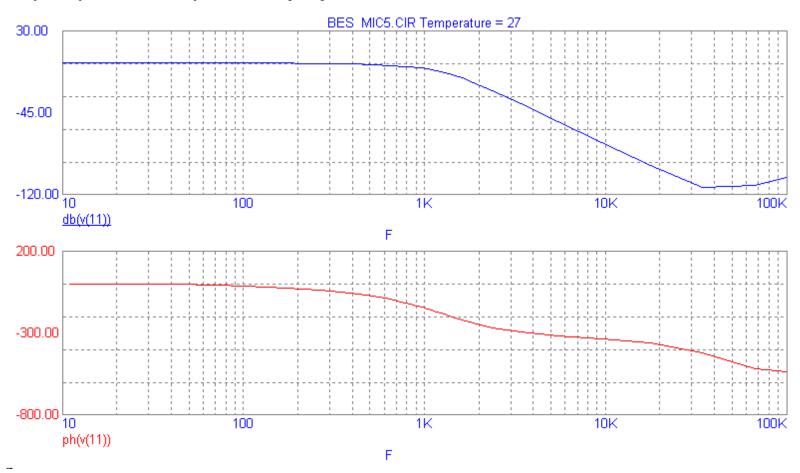

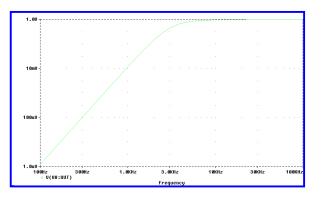

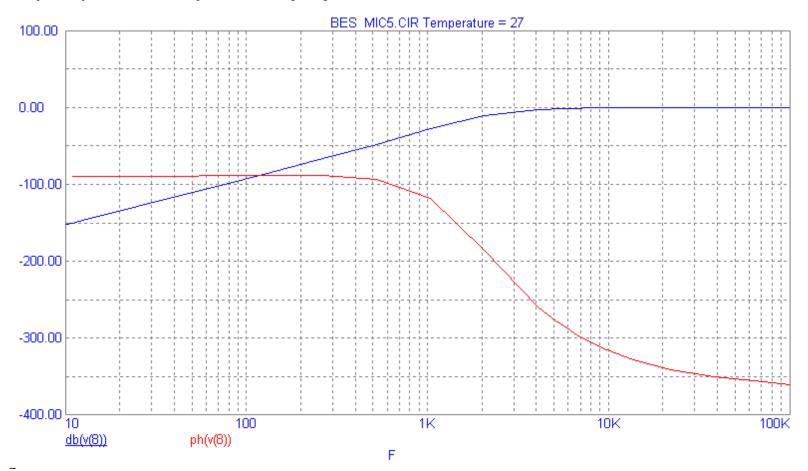

#### shown in figure 4-3, the AC simulation results are shown in figure 4-4.

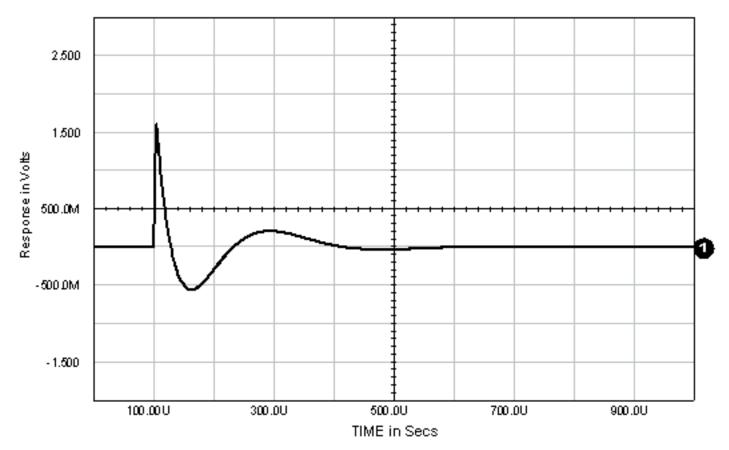

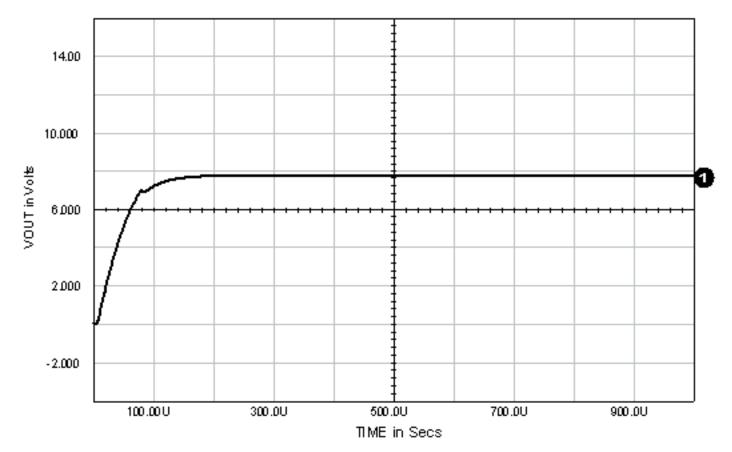

Figure 4-3: IsSpice filter response to step input

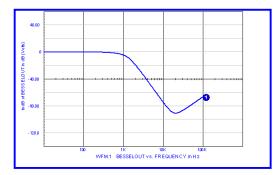

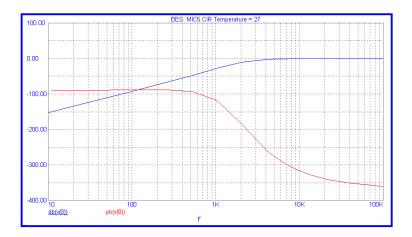

Figure 4-4: IsSpice AC filter response

The evaluation version of Pspice has a model for the LM324, but the default model had an error in it. The UA741 opamp model was used in its place. The operation amplifier does not play a critical role in this circuit because of the slow response of the circuit. The limiting parameter of the delay time is the RC time constant and not the slew rate or drive capability of the operational amplifier. The Pspice model response to a step input is shown in figure 4-5, and the AC results are shown in figure 4-6.

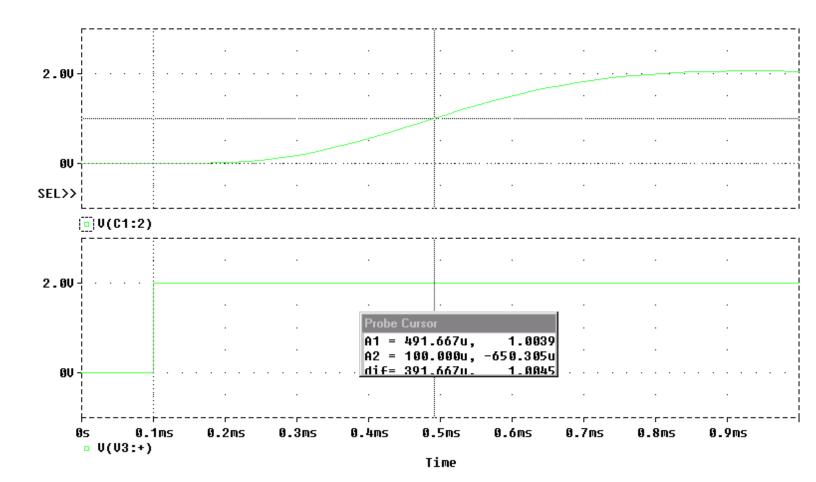

Figure 4-5: Pspice filter response to step input

Figure 4-6: Pspice AC filter response

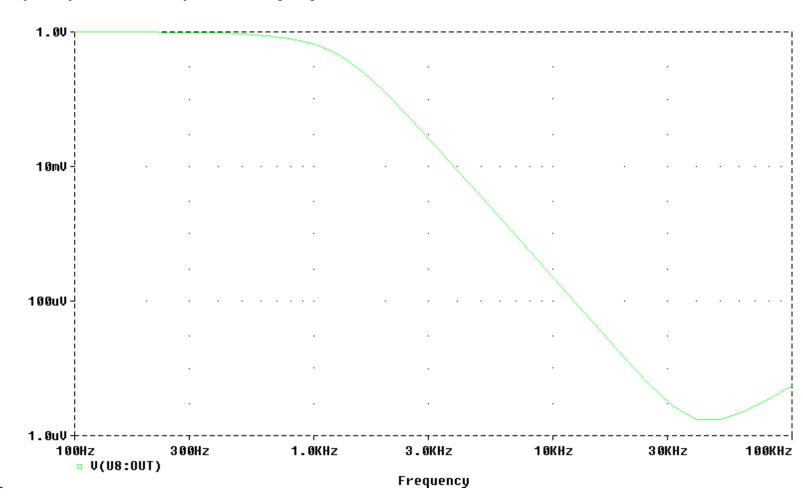

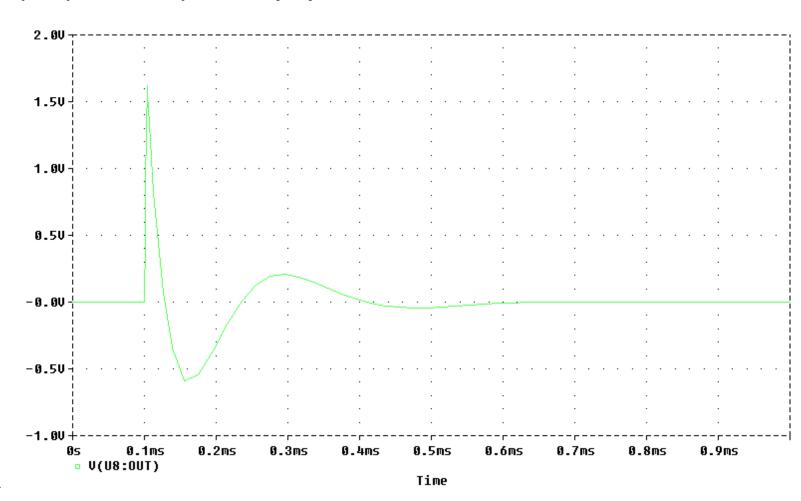

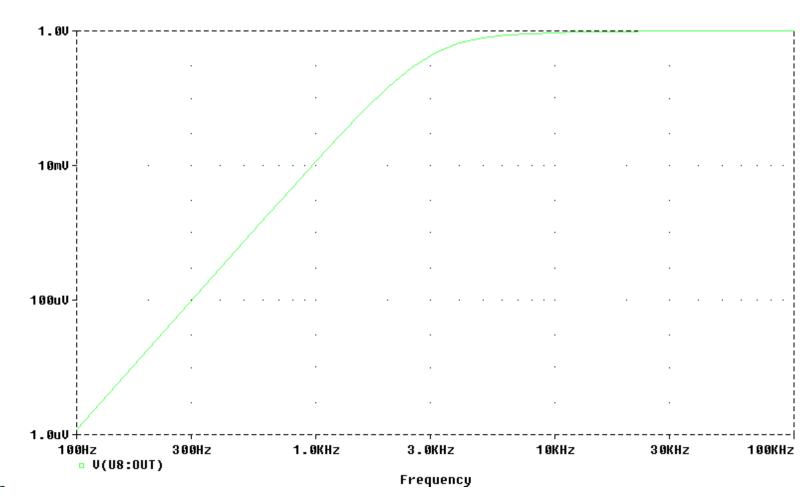

Micro-cap V also had an LM124 model. The model response to a step input is shown as figure 4-7, and the AC results are shown as figure 4-8.

Figure 4-7: Microcap filter response to step input

Figure 4-8: Microcap AC filter response

Bessel-Thompson Delay low pass filter

| Run Time Summary |              |                |  |  |

|------------------|--------------|----------------|--|--|

| IsSpice v 7.6    | PsPice v 6.3 | Micro-Cap V v2 |  |  |

| 5.6 Sec          | 2.37 Sec     | 16.5 Sec       |  |  |

Disadvantages: Rounds off signal and places importance on detection device.

Filenames: bessel (IsSpice) besmc5 (Micro-cap) bes\_ps (Pspice)

Copyright 2002, PCBCafe. 1-888-44-WEB-44 http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image762.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image765.gif

## http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image768.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image768.gif [19/01/2002 22:01:38]

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image769.gif

Bessel-Thompson Delay low pass filter with pulse shaper

## with pulse shaper

Expedition<sup>™</sup> Series

equest a free CD tod

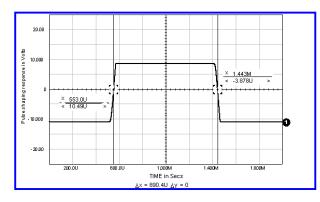

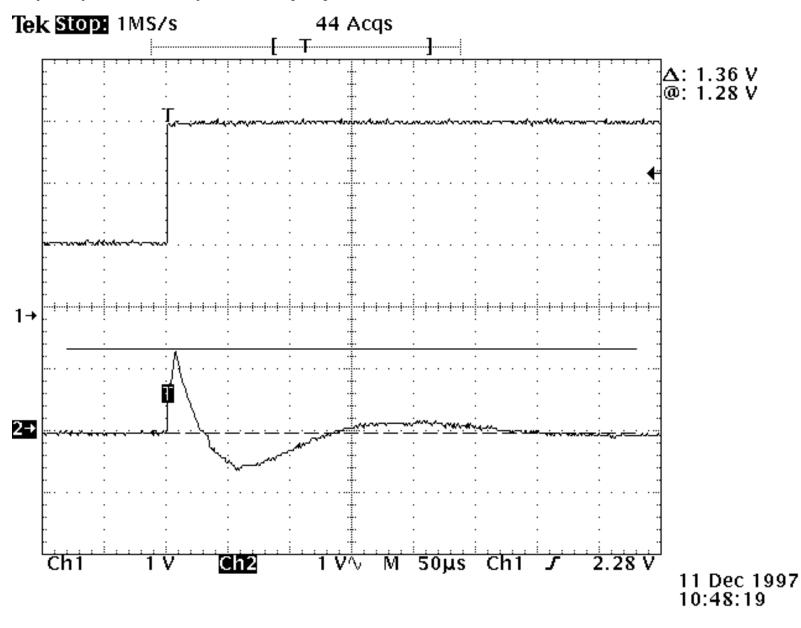

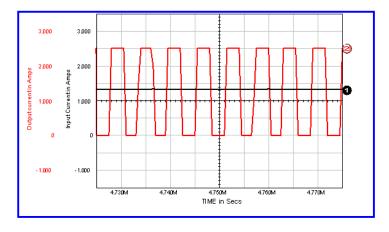

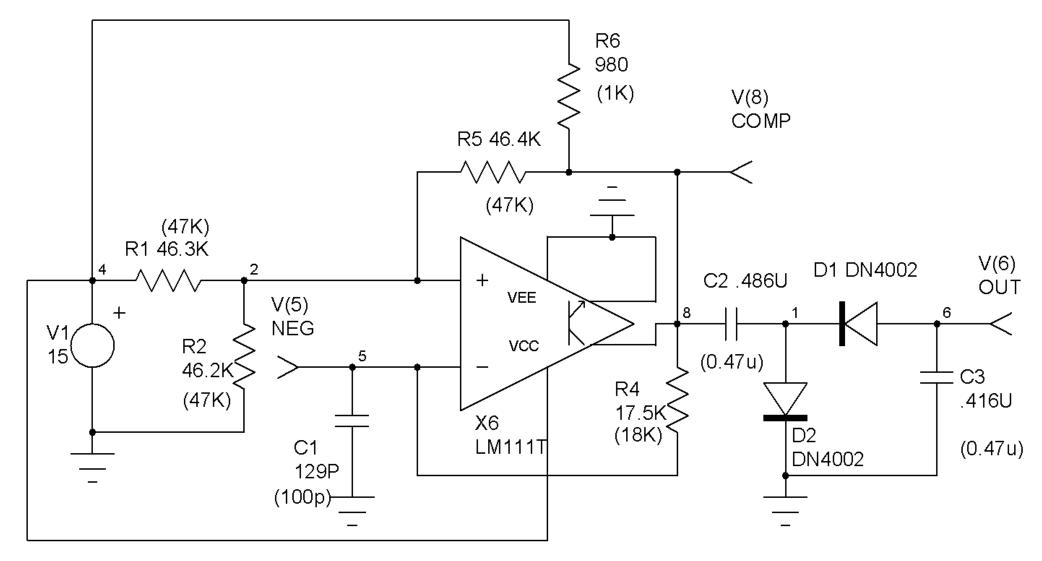

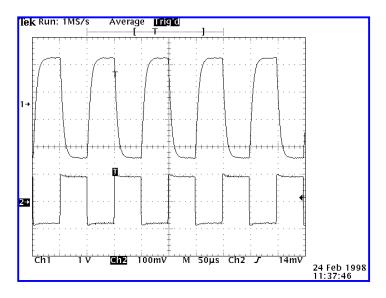

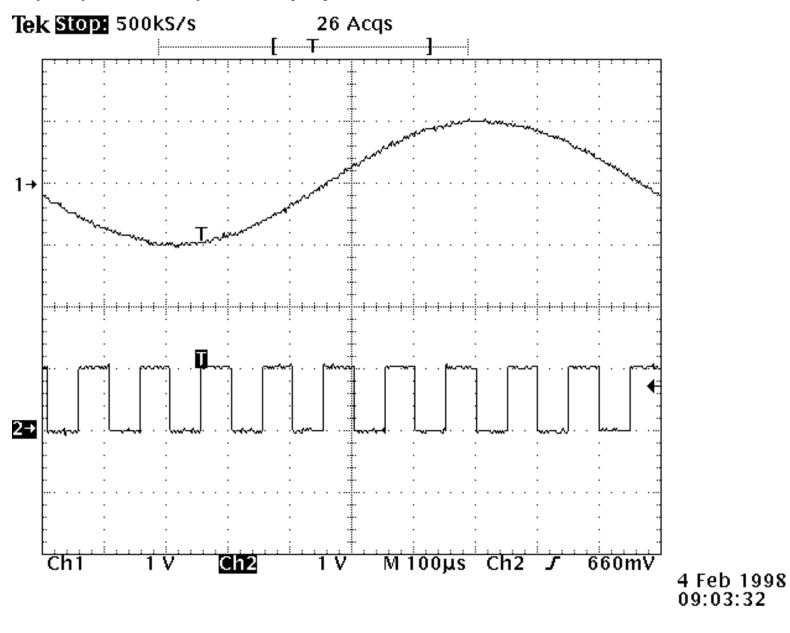

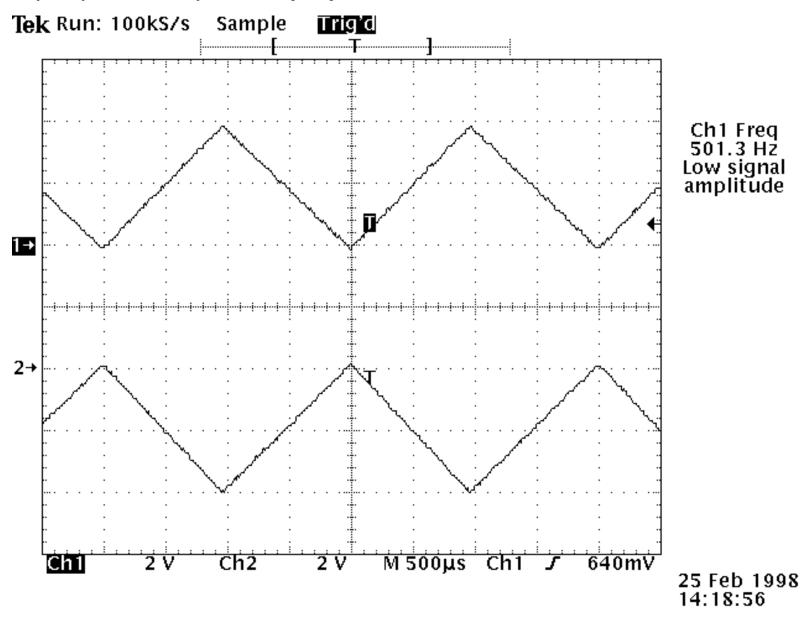

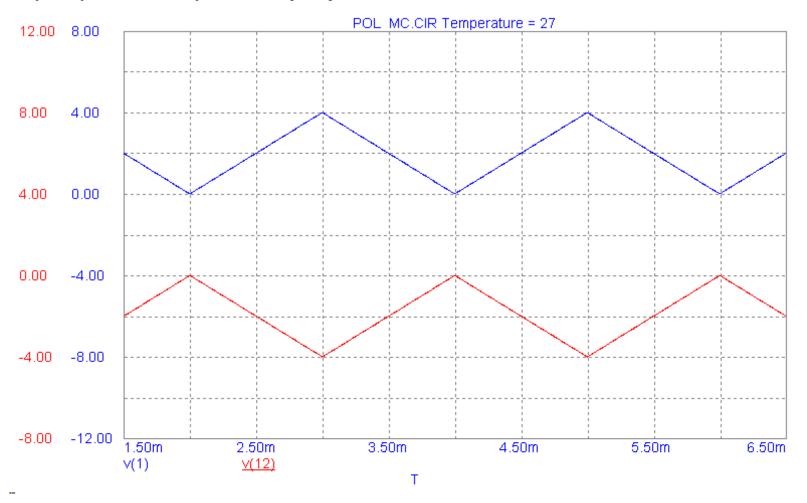

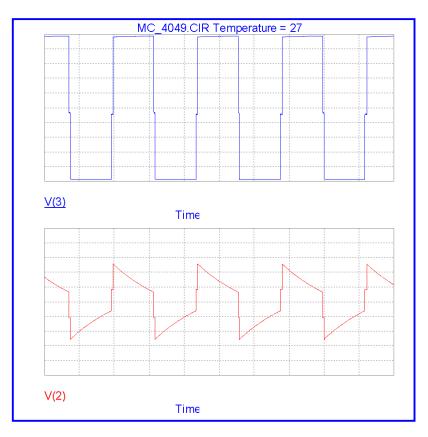

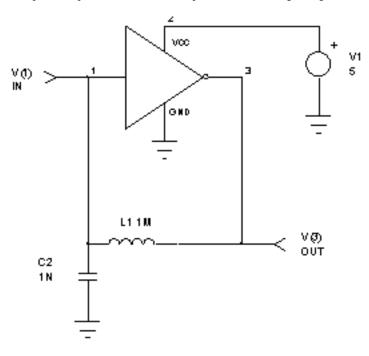

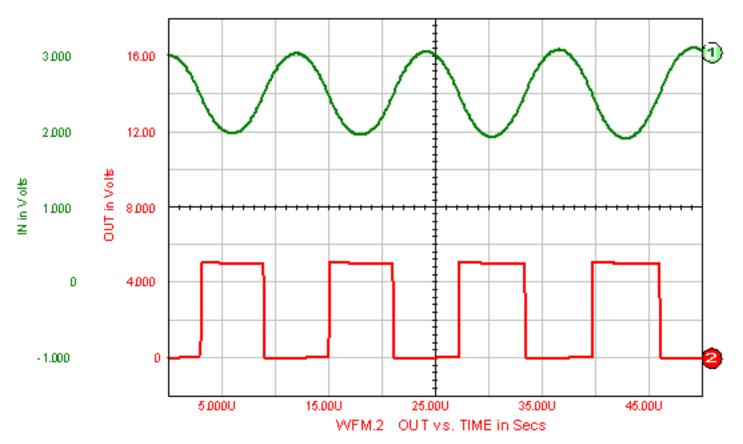

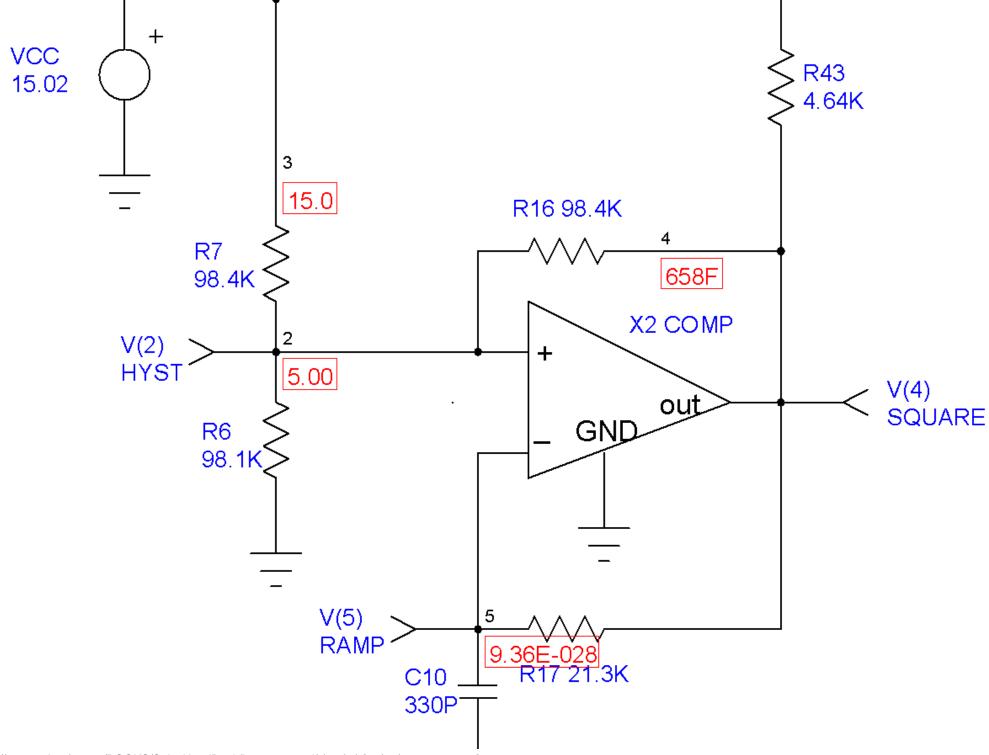

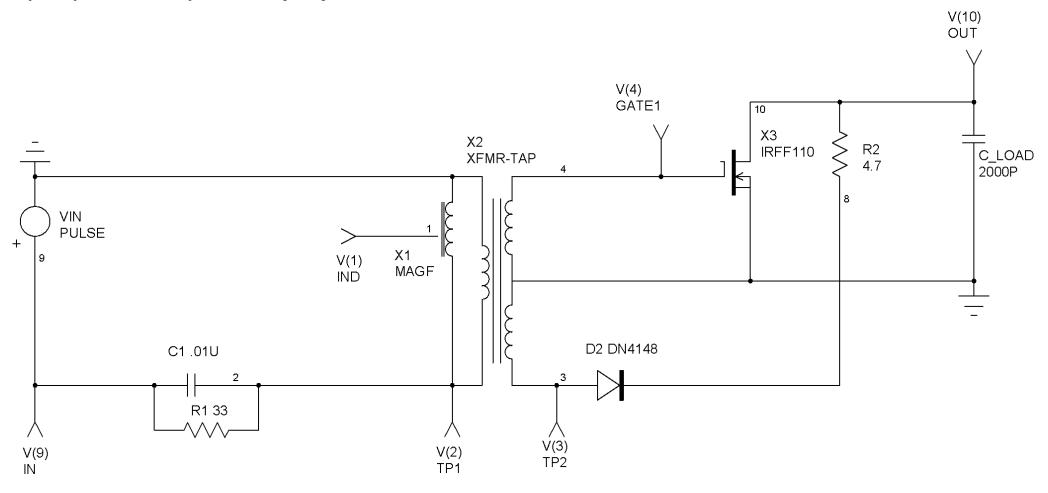

A simple pulse shaping modification can be added to the Bessel-Thompson delay filter using an additional operational amplifier. Using resistors to divide down the supply voltage to half the output voltage of the delay filter, then comparing it to the delay filters response results in a time delayed square wave. The schematic of this circuit is shown in figure 5-1. This simulation also allows us to compare the operational amplifier models that came with each software package. The response of this circuit is driven from rail to rail providing the saturation voltages of the models. Also the slew rate of the output should be consistent with the measured and published data. Keep in mind that these parameters may not be consistent between brands and between lots, and they should be consistent with the average data from the manufacturer designed after.

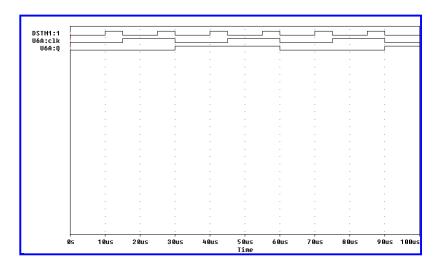

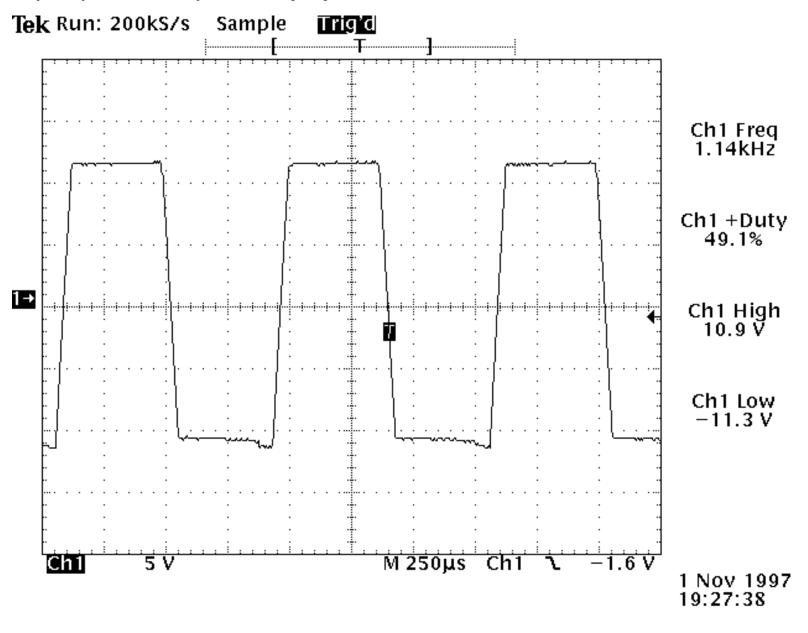

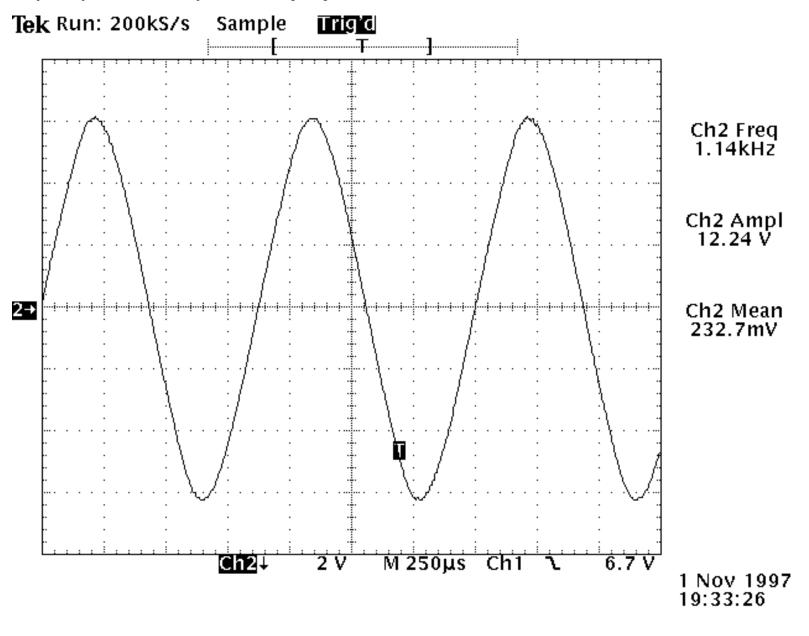

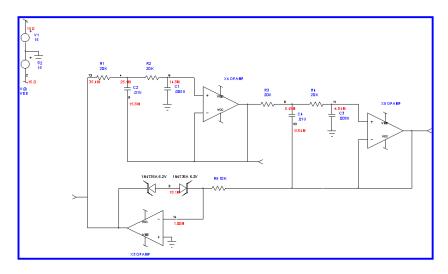

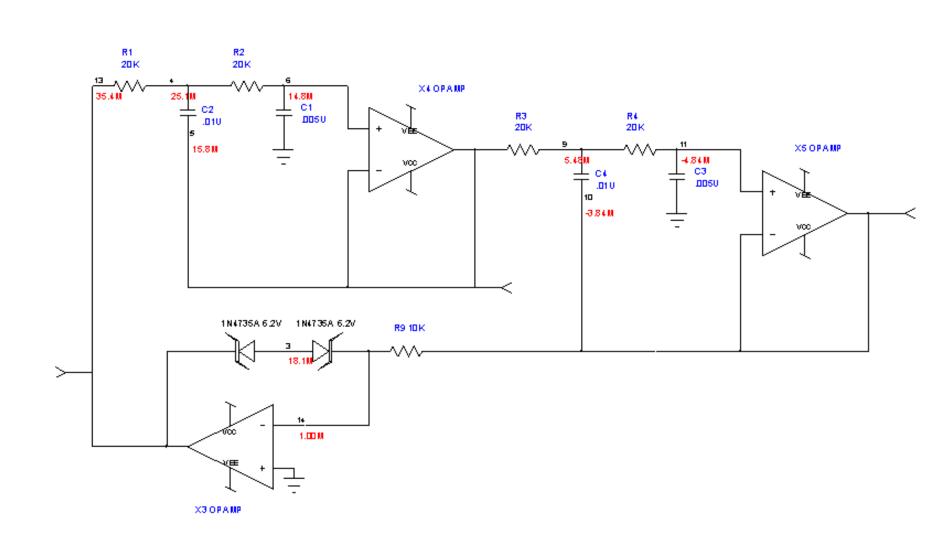

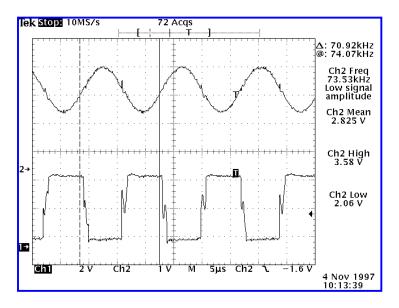

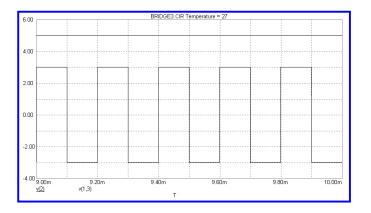

Figure 5-1: Bessel-Thompson delay filter with shape reformation

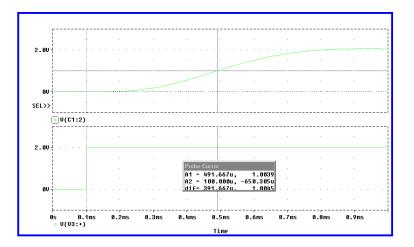

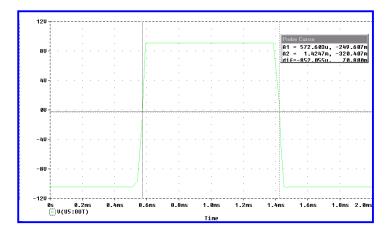

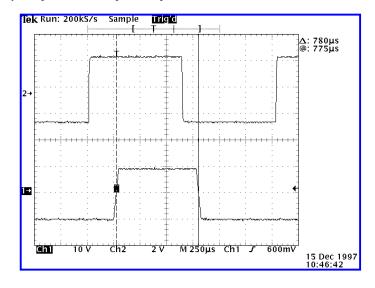

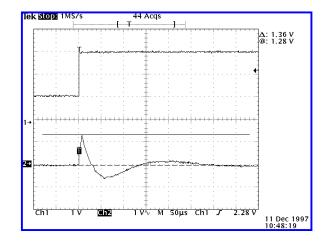

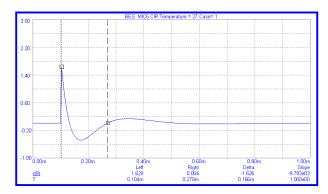

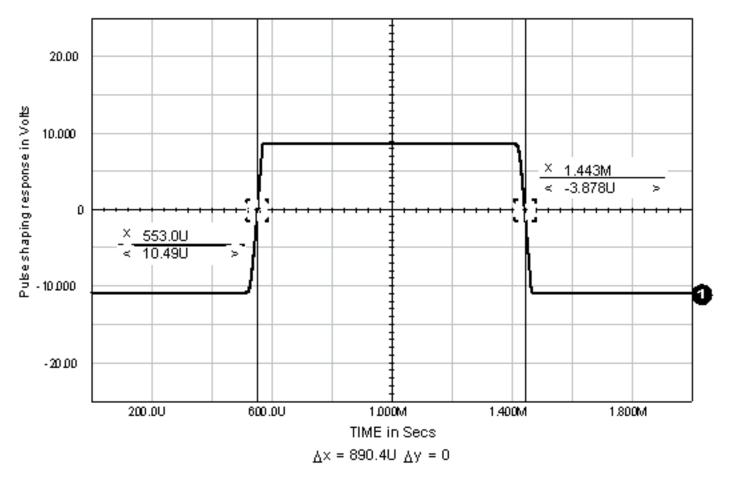

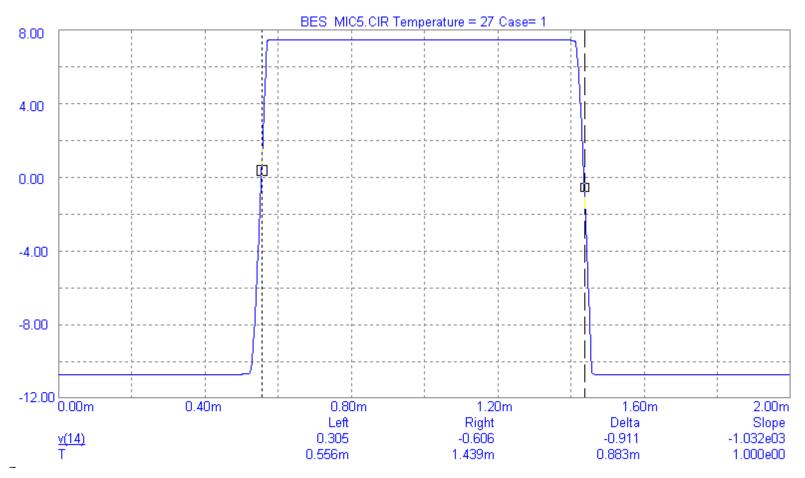

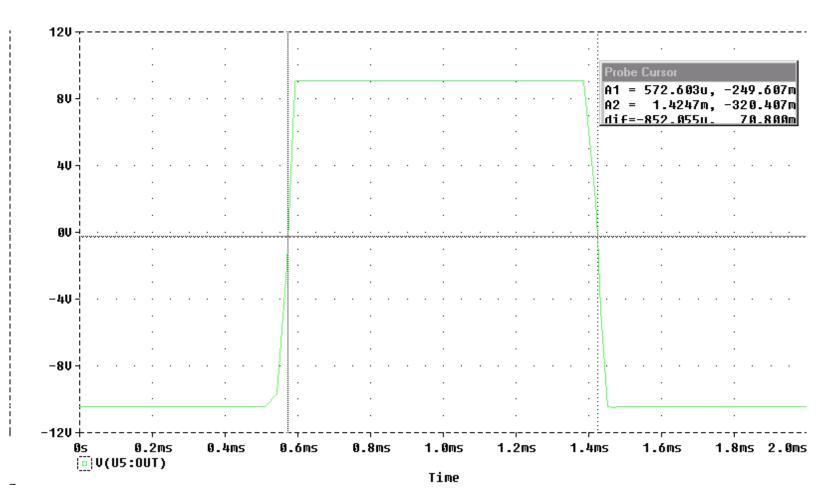

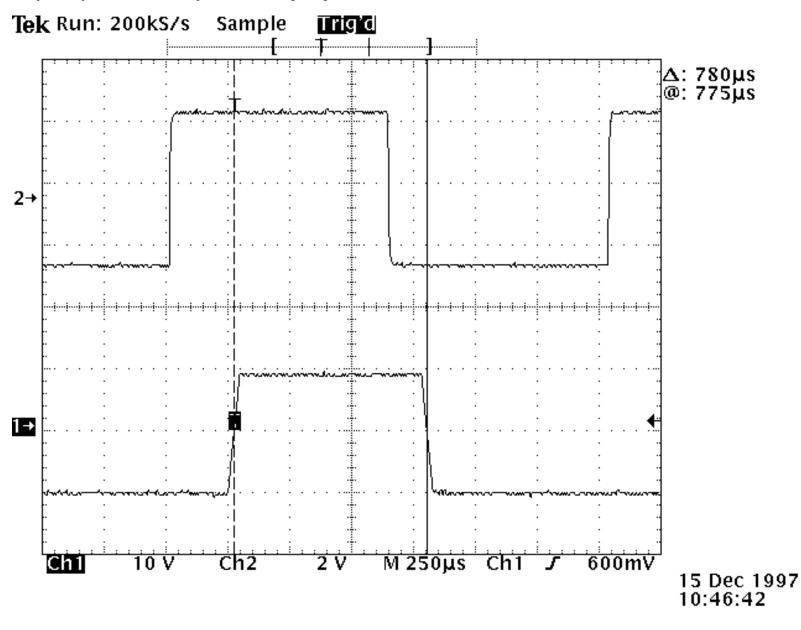

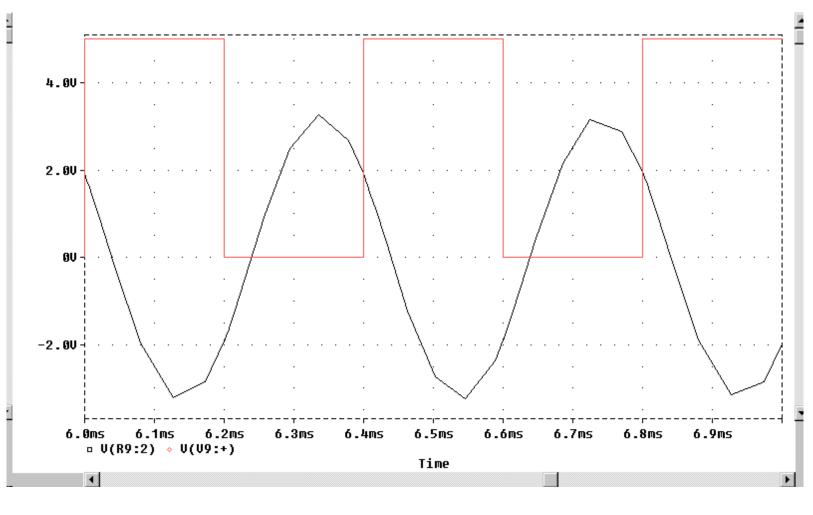

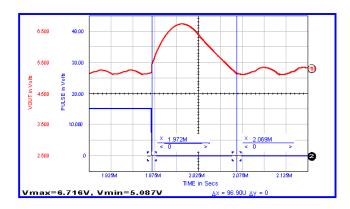

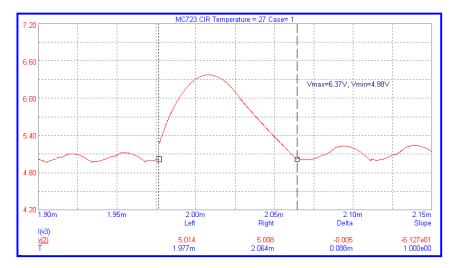

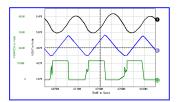

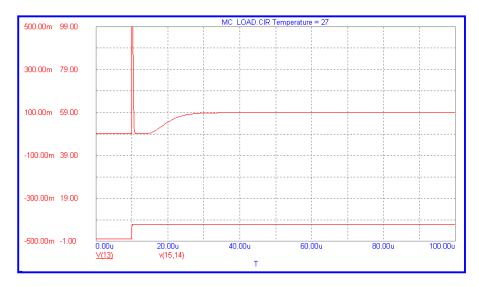

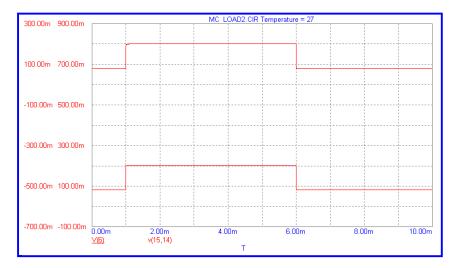

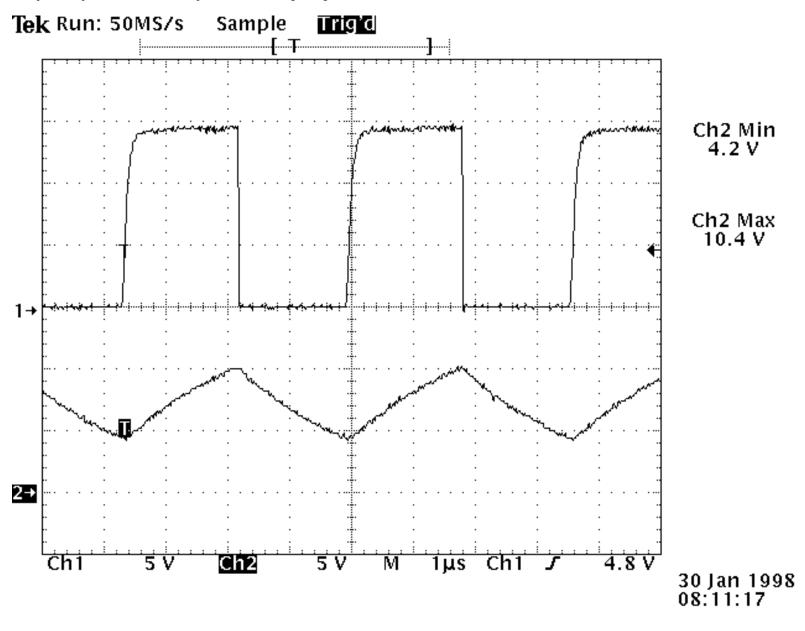

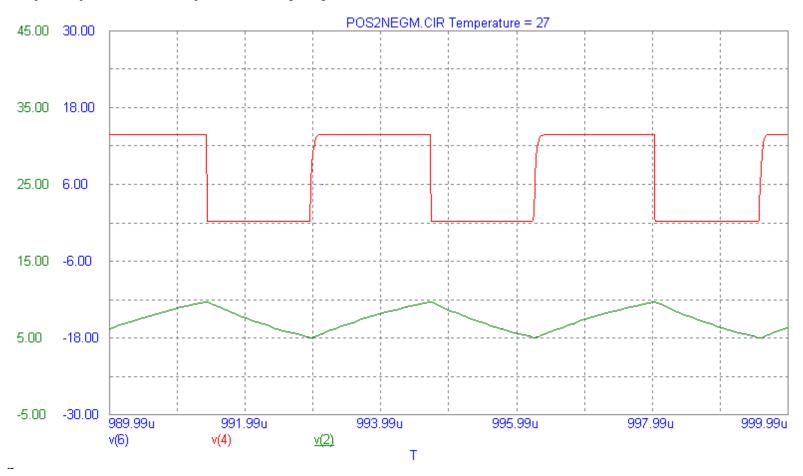

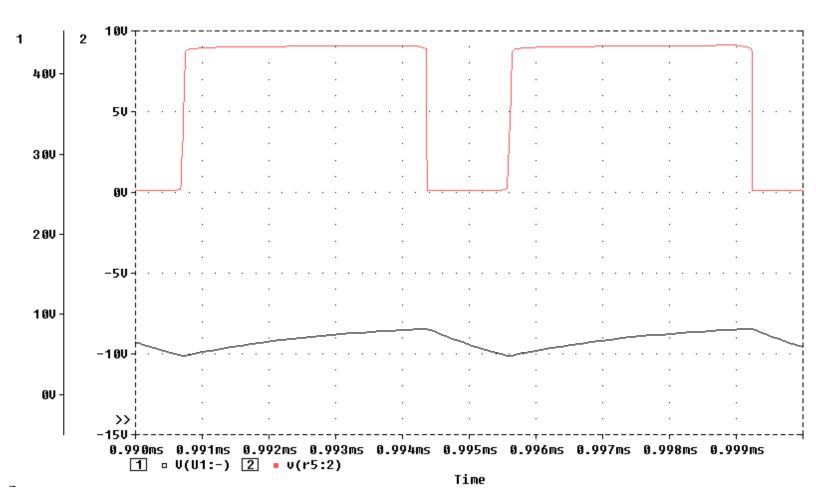

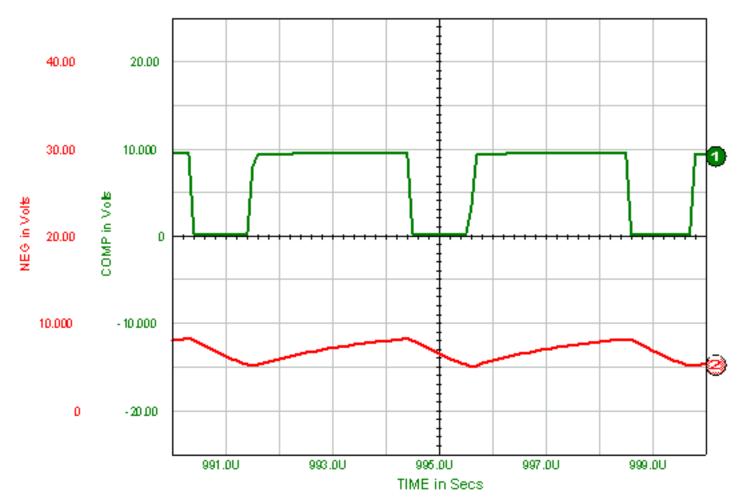

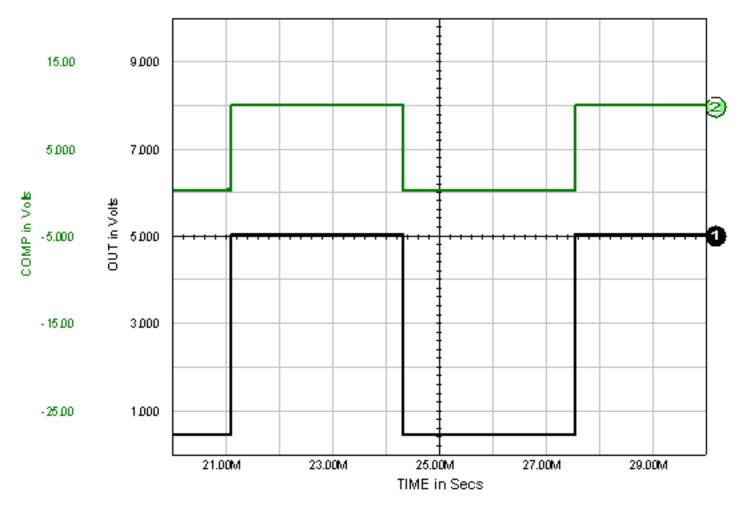

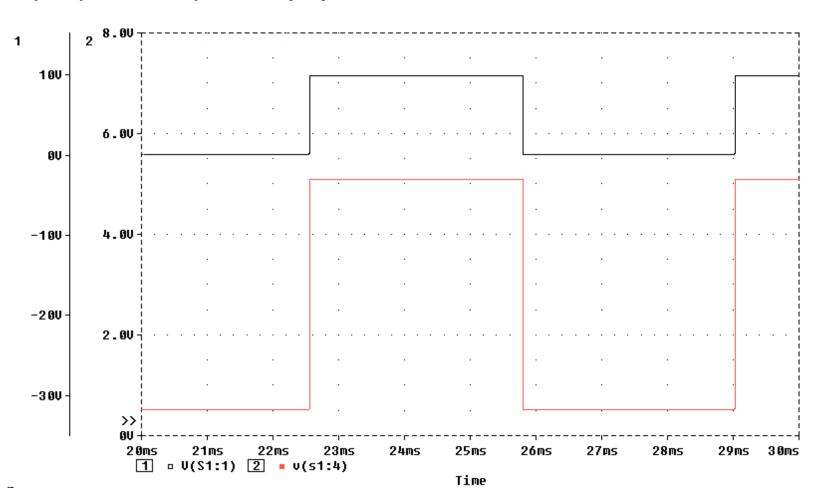

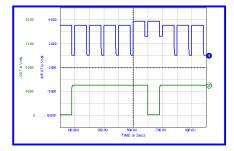

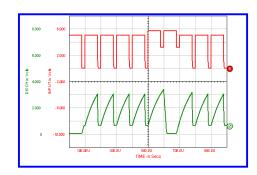

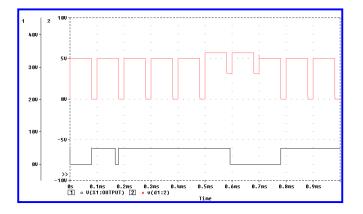

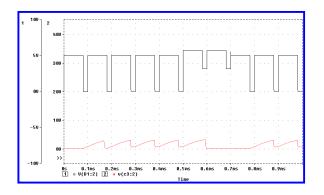

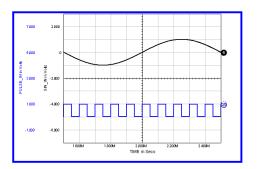

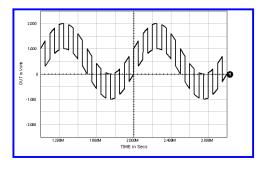

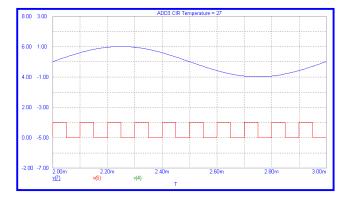

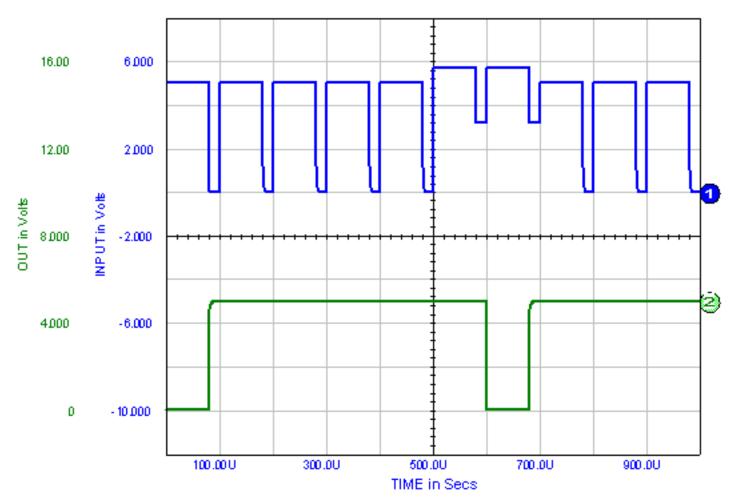

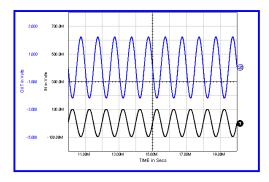

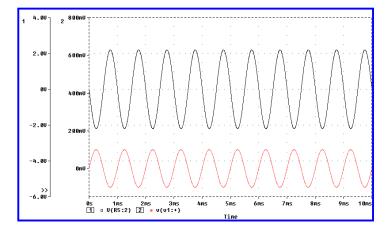

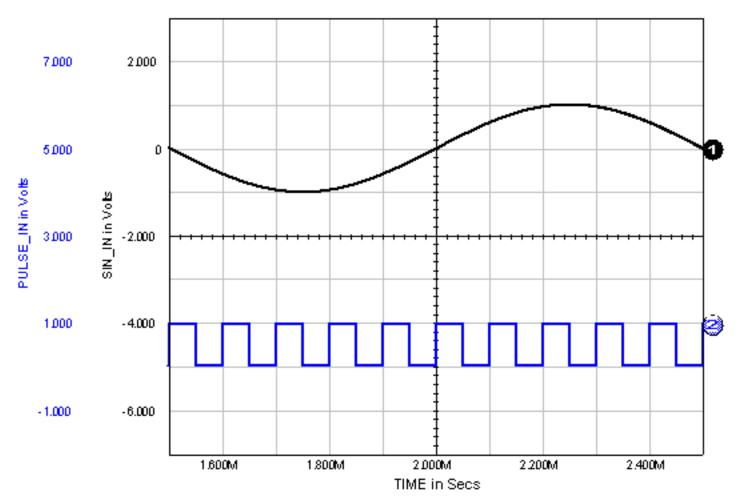

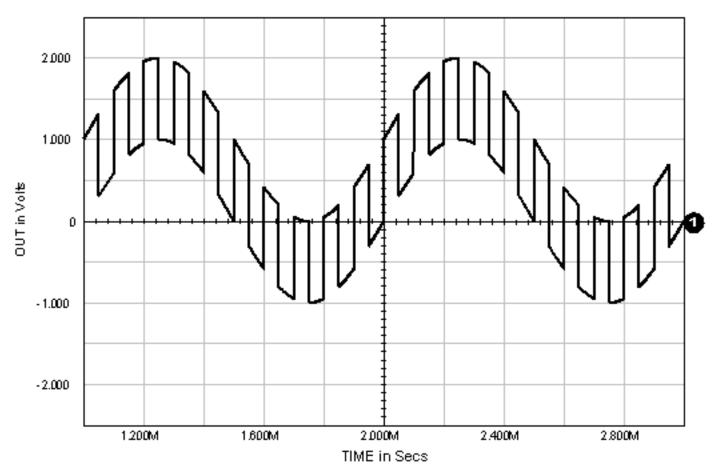

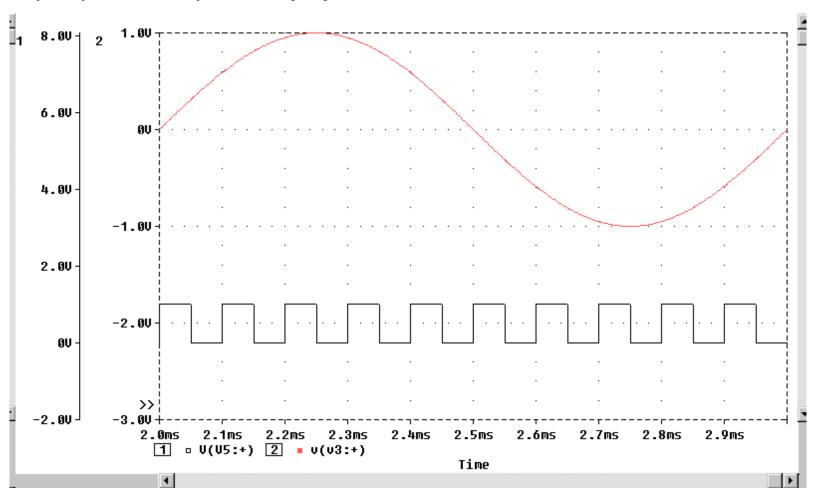

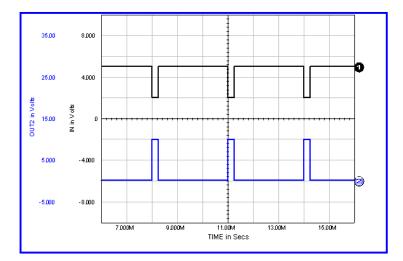

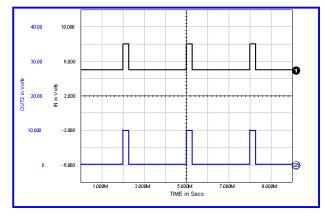

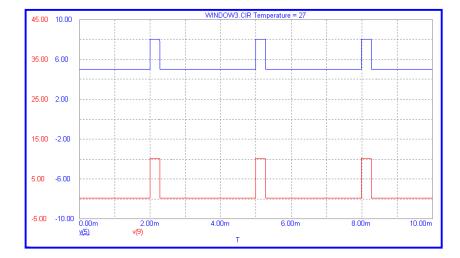

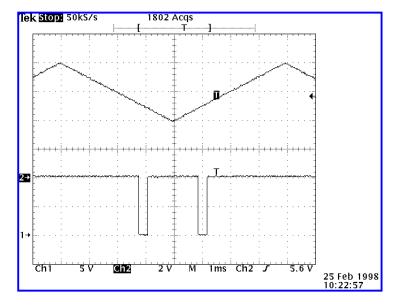

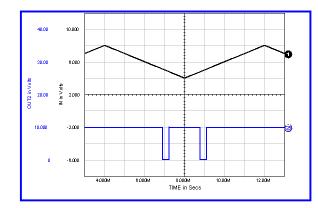

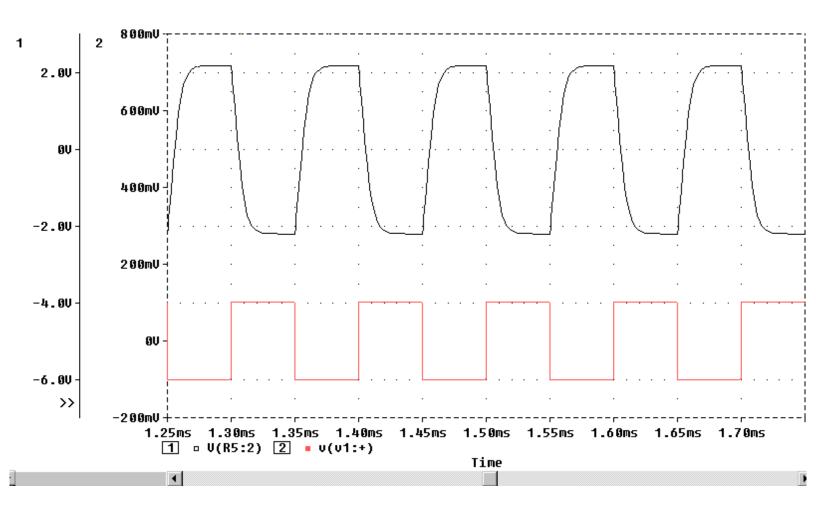

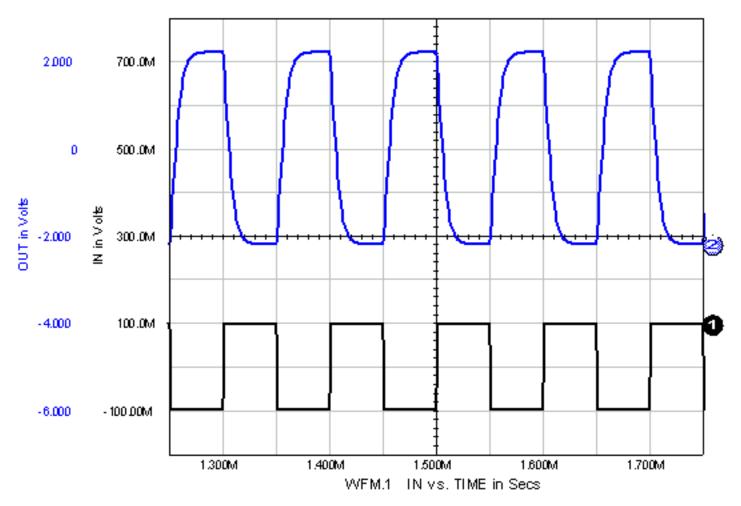

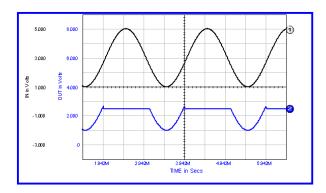

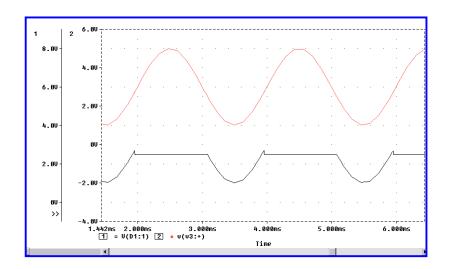

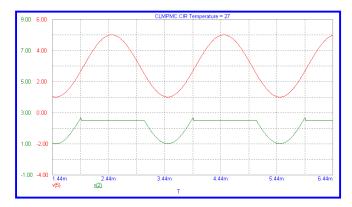

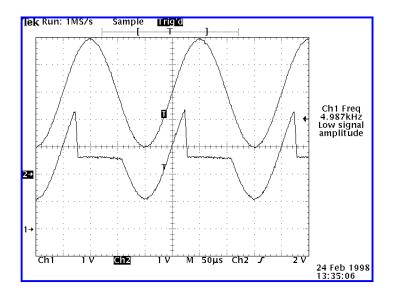

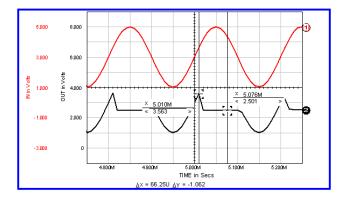

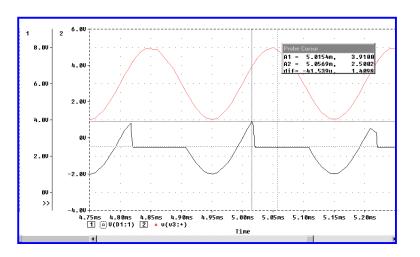

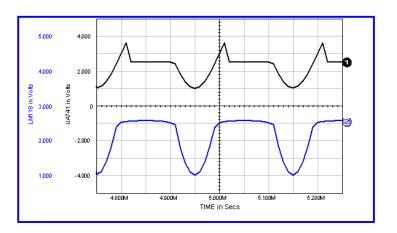

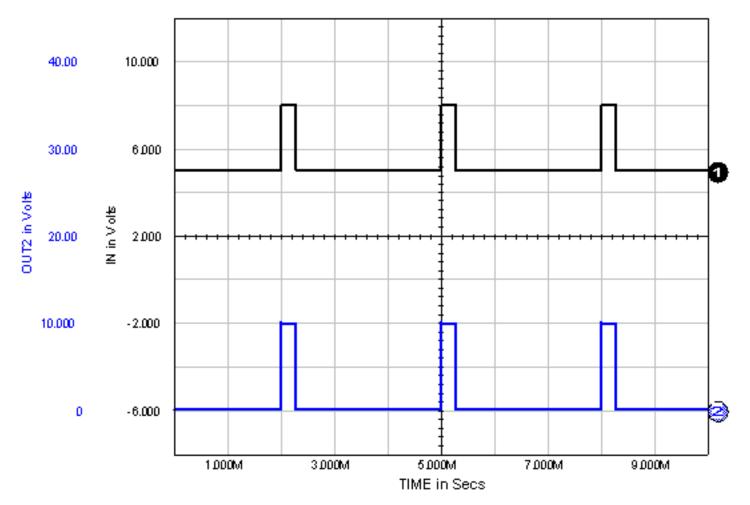

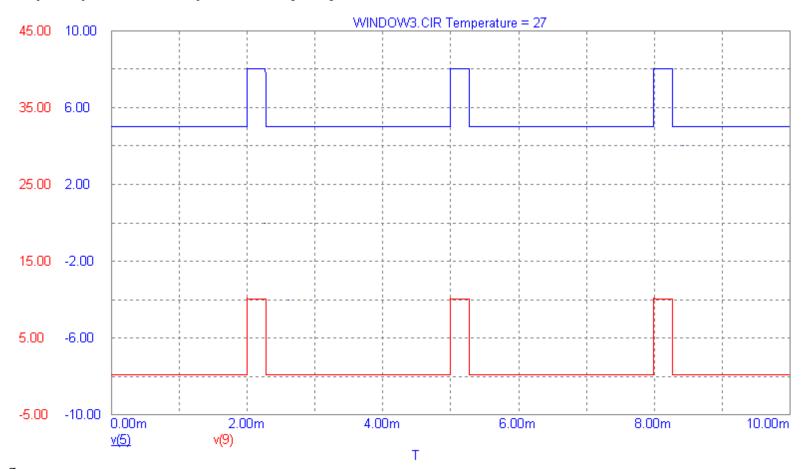

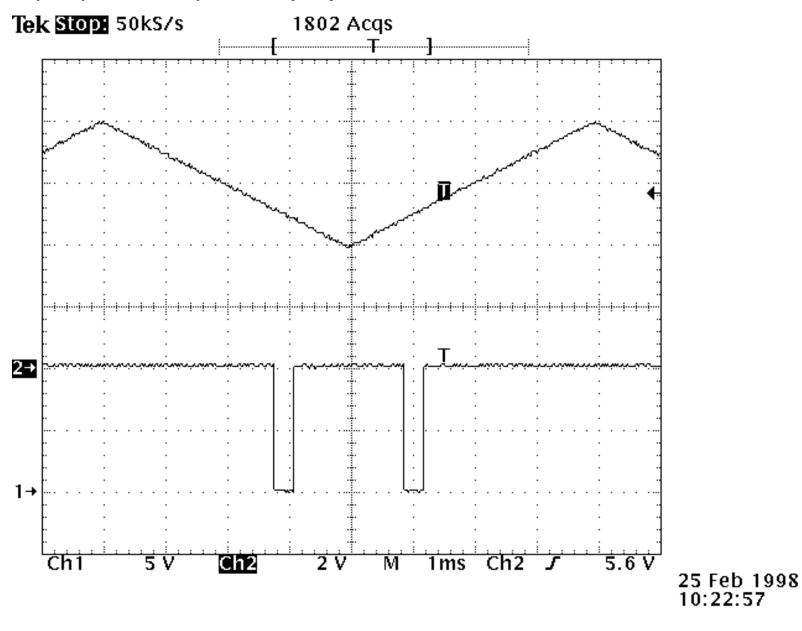

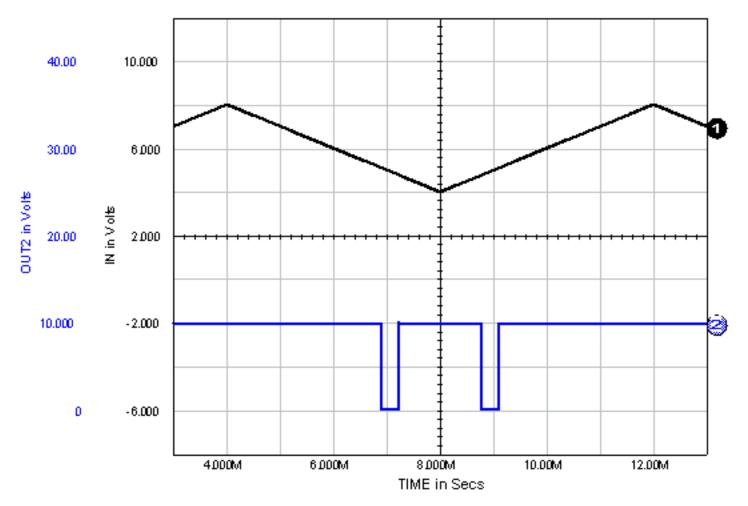

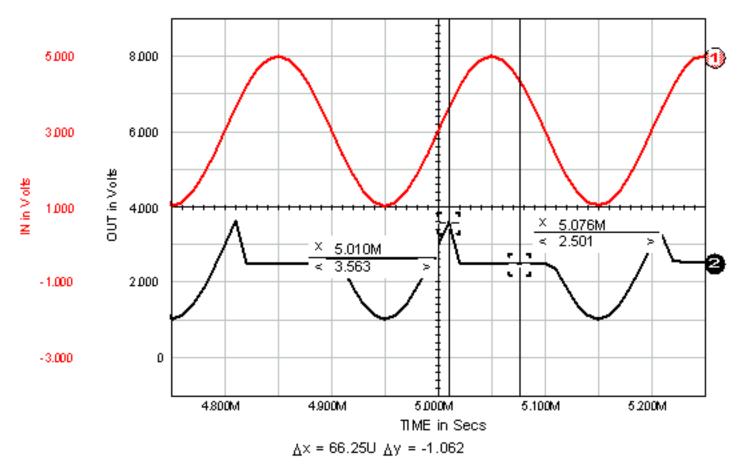

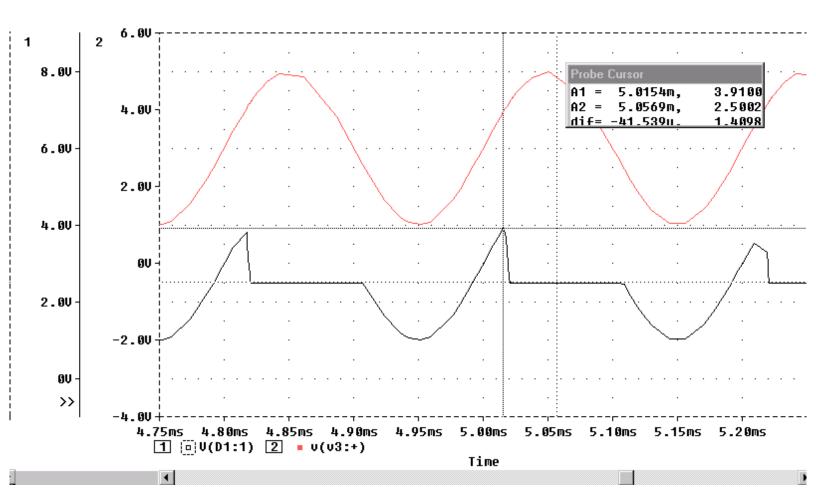

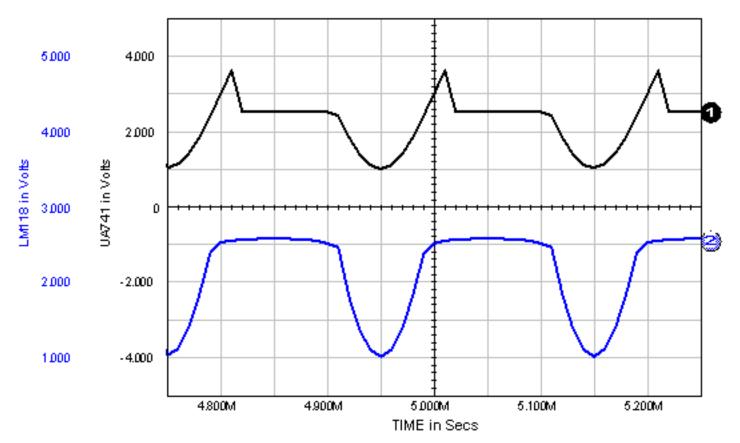

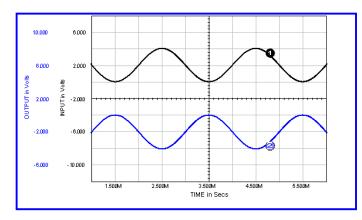

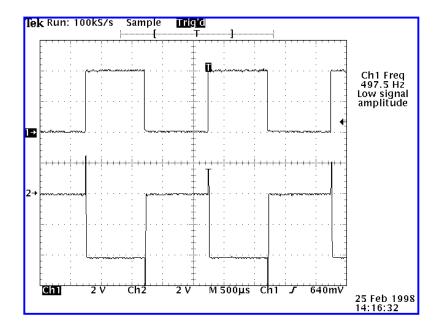

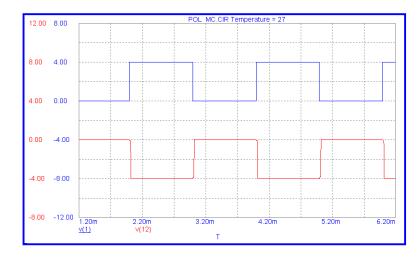

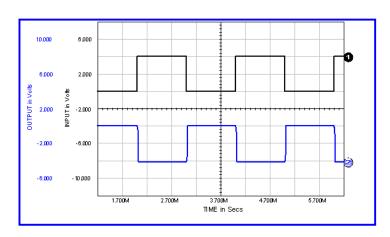

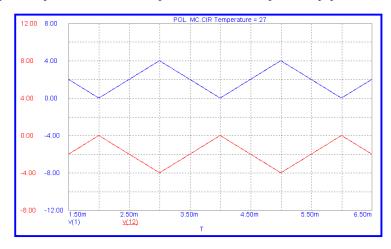

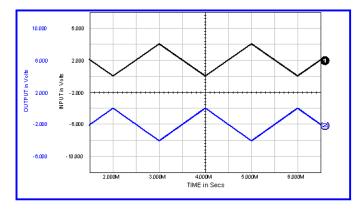

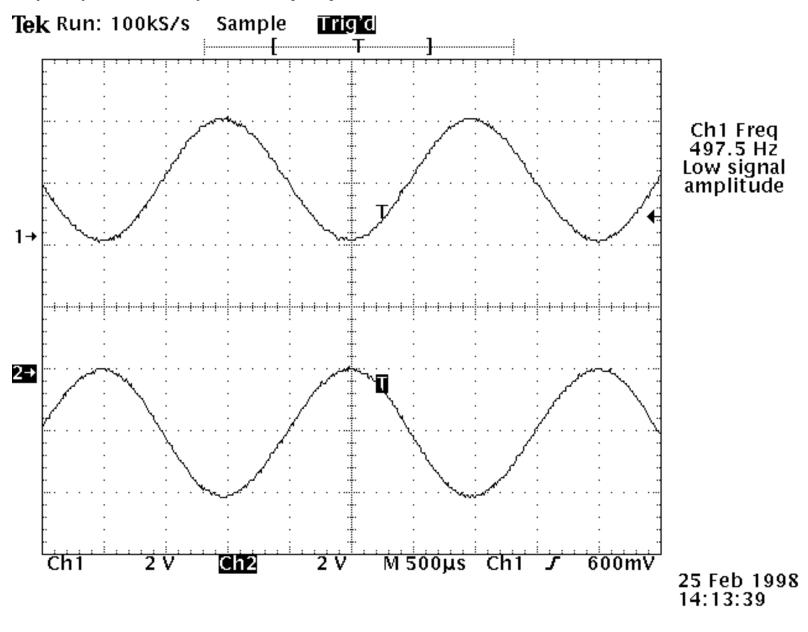

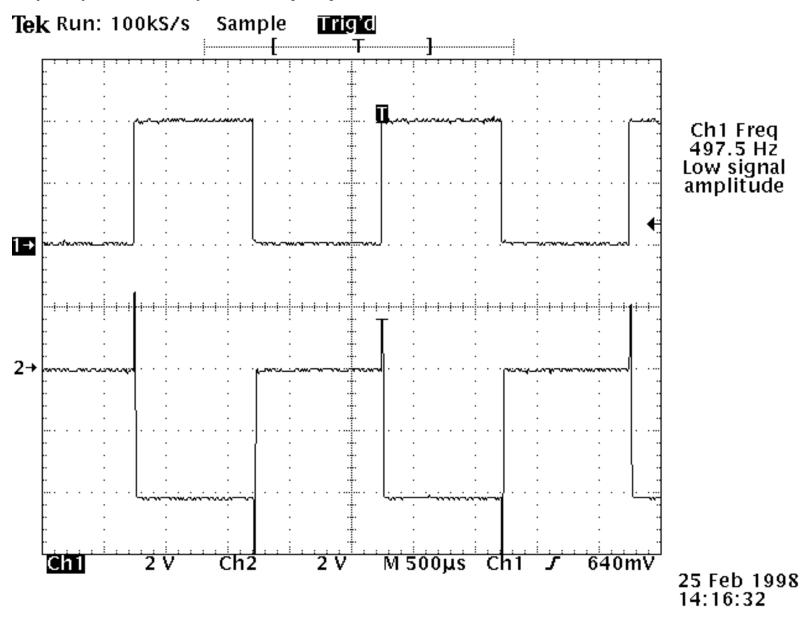

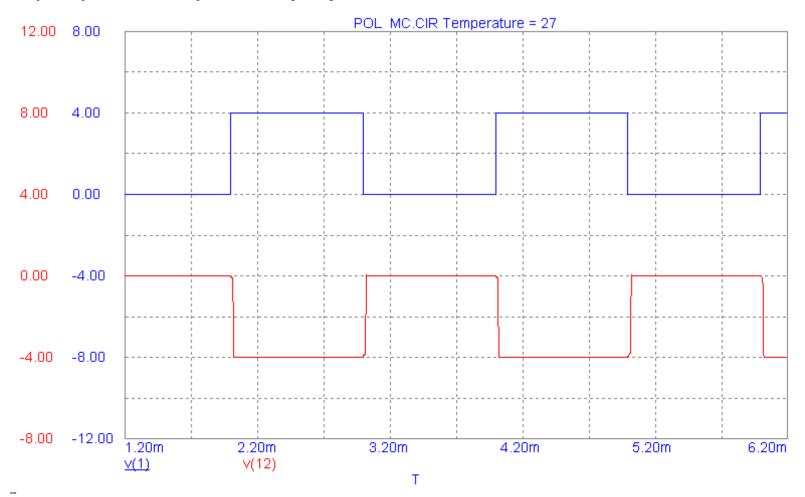

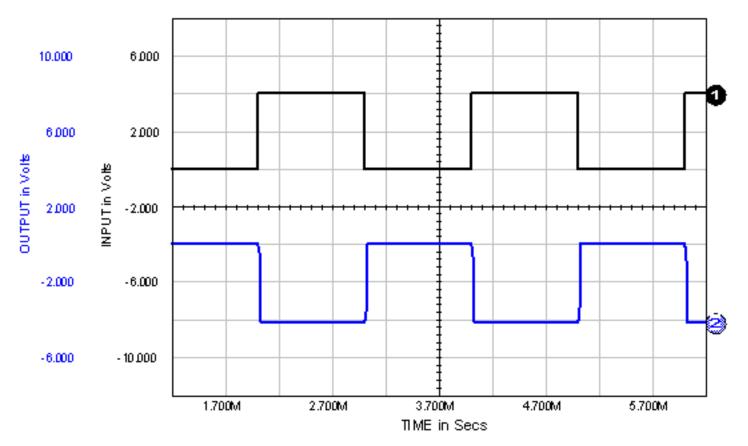

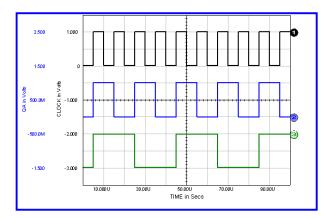

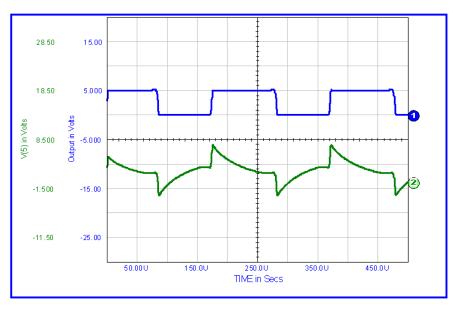

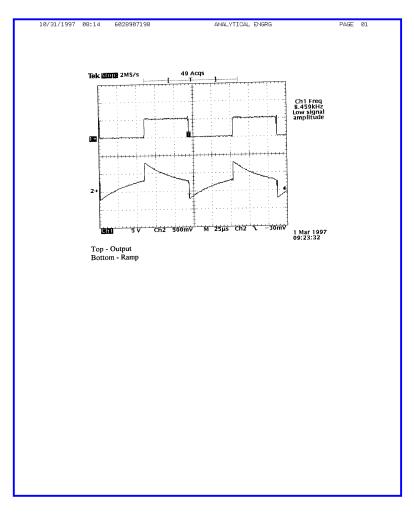

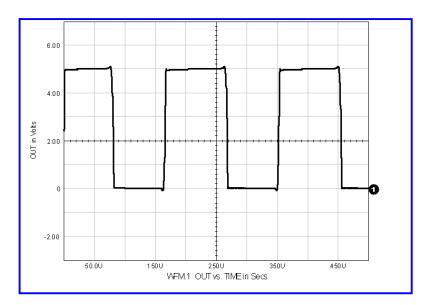

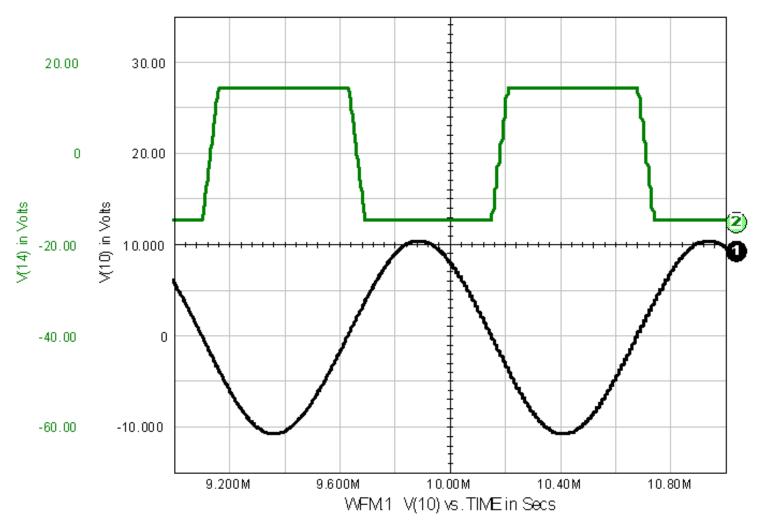

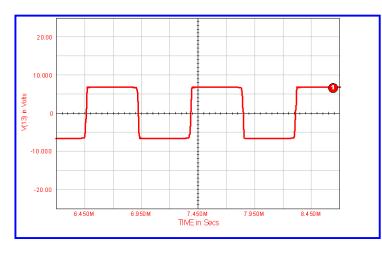

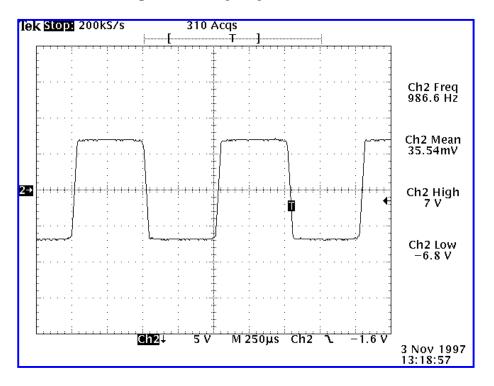

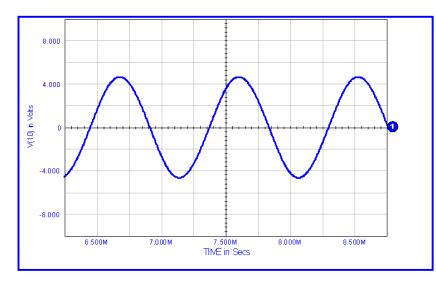

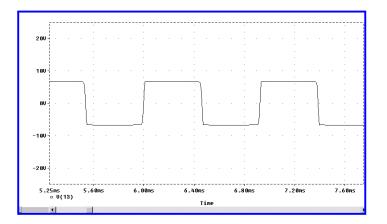

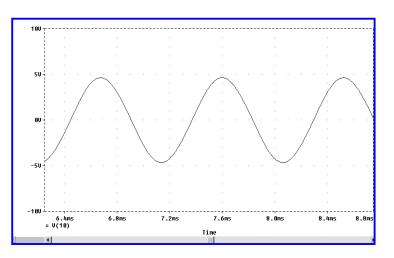

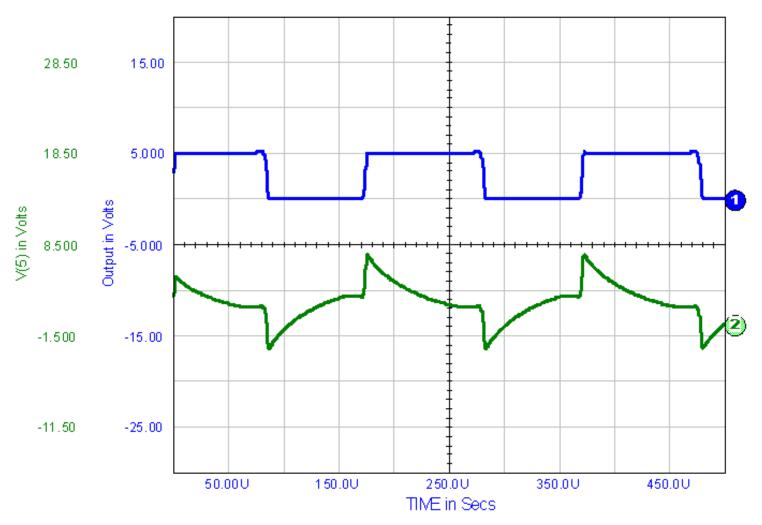

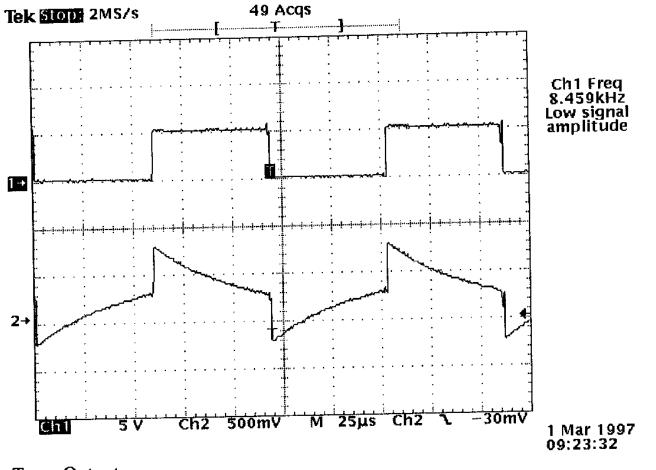

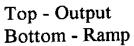

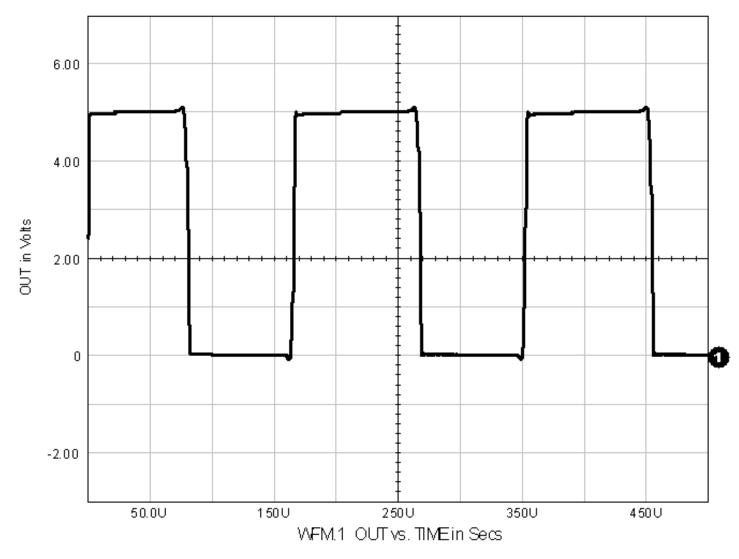

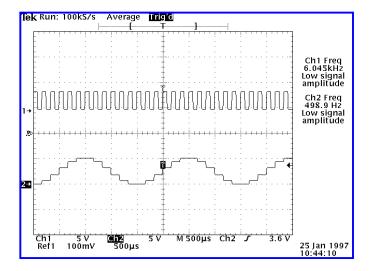

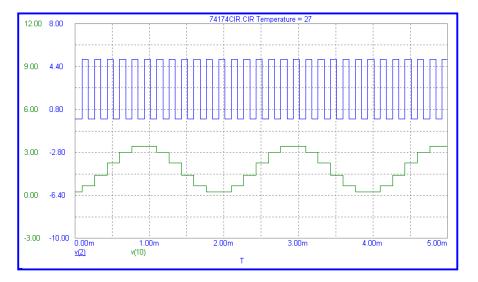

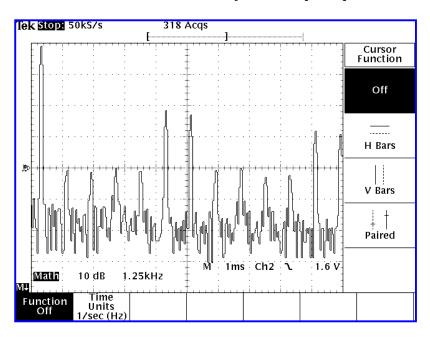

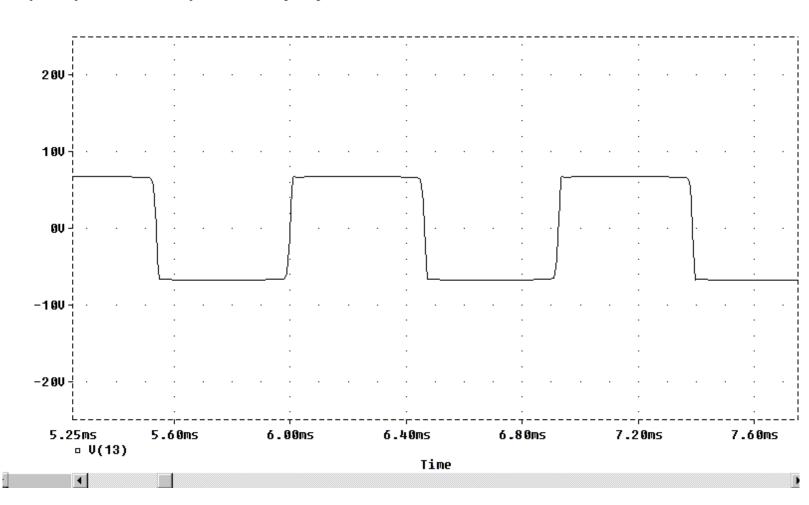

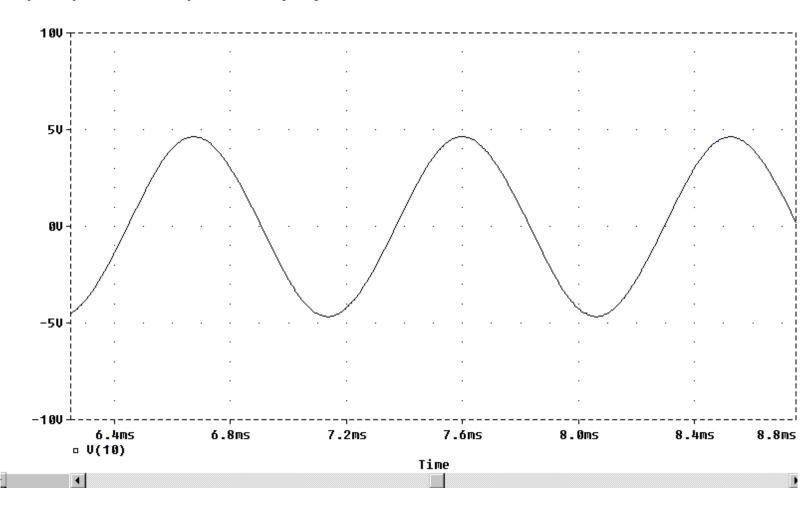

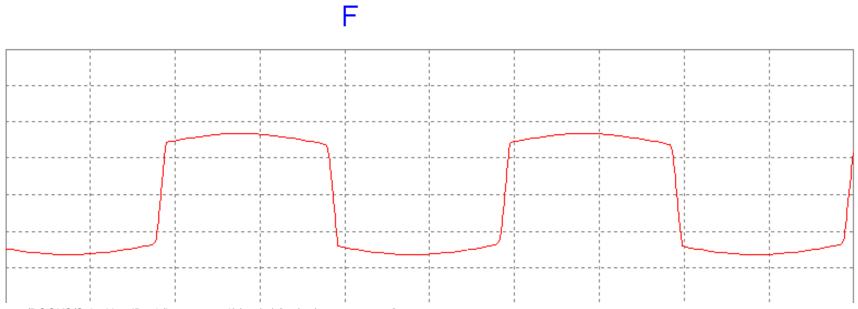

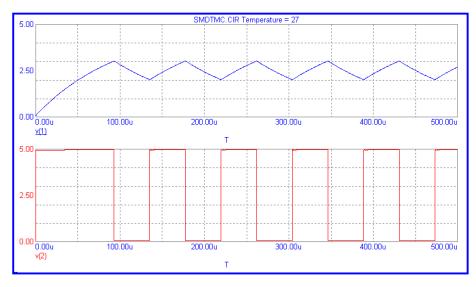

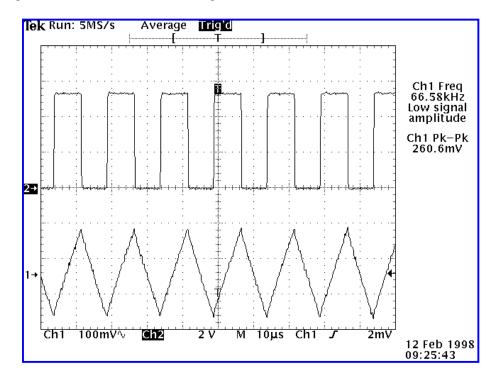

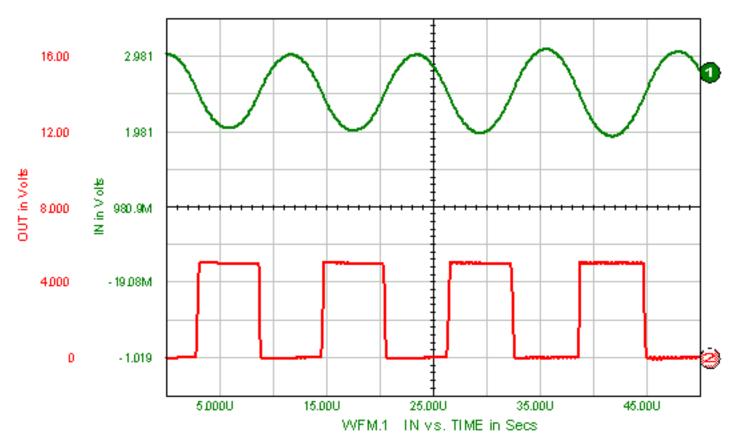

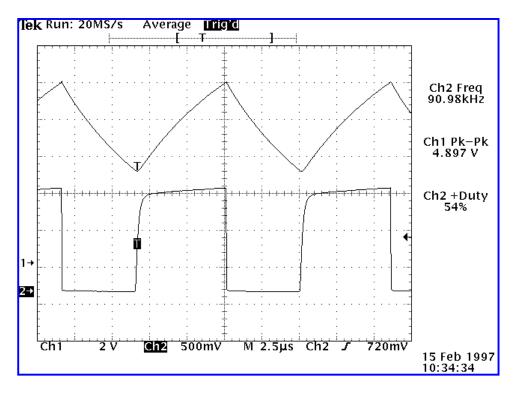

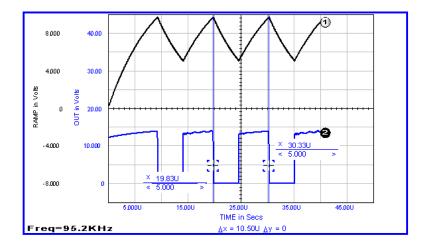

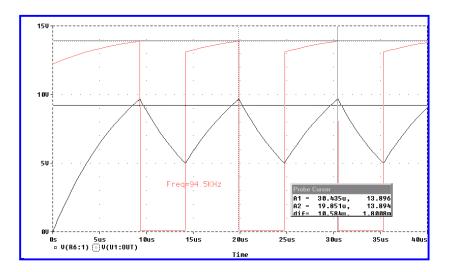

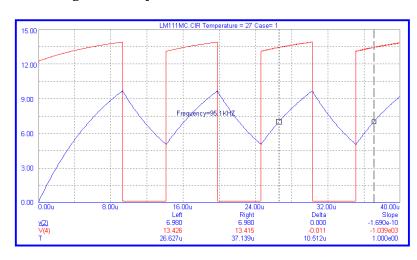

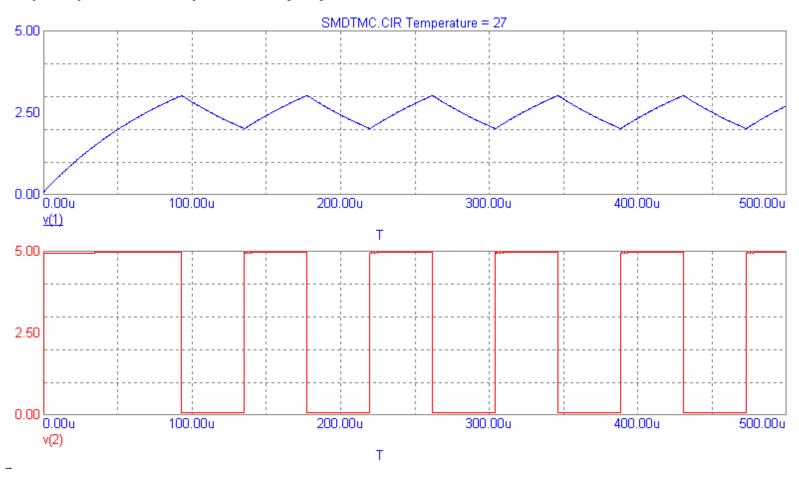

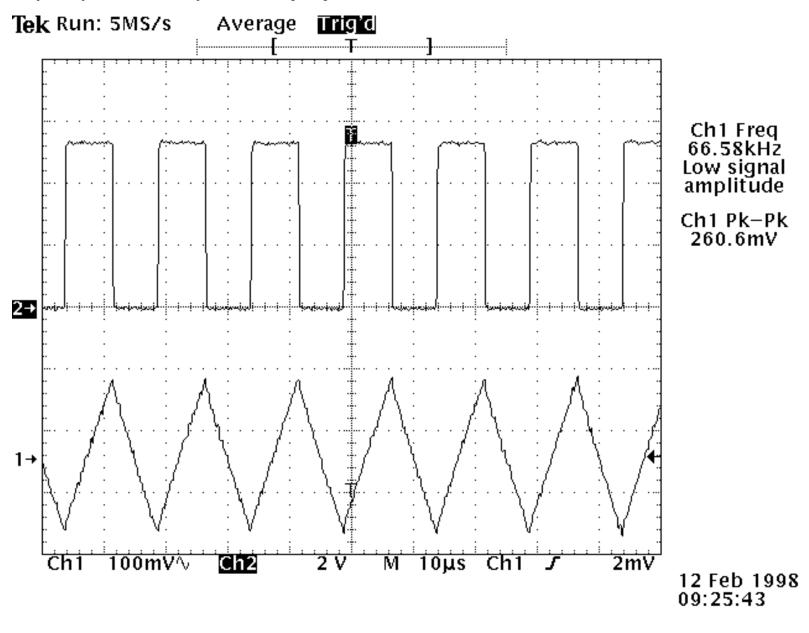

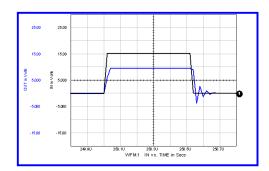

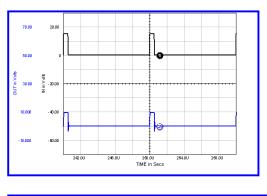

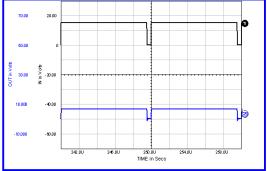

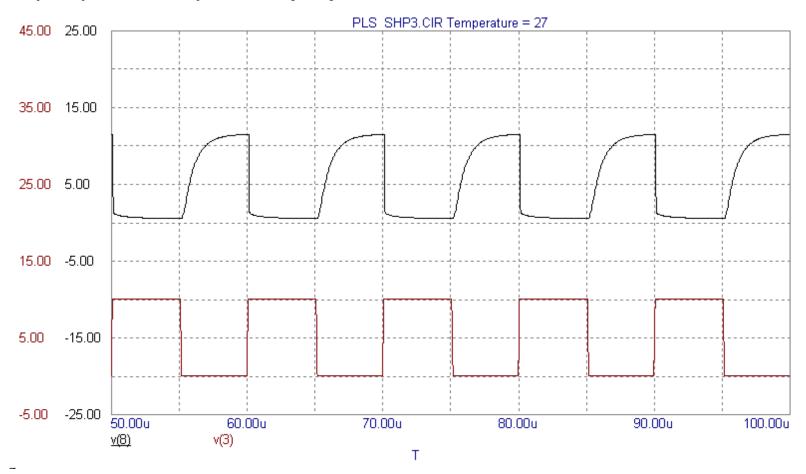

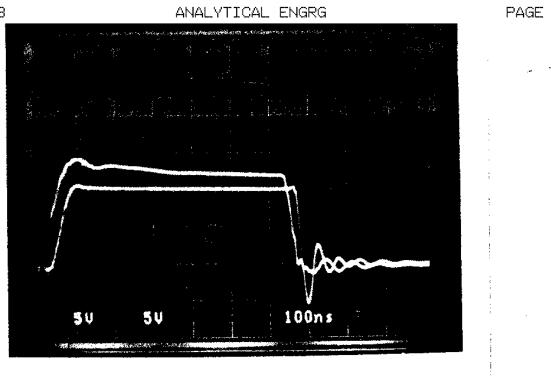

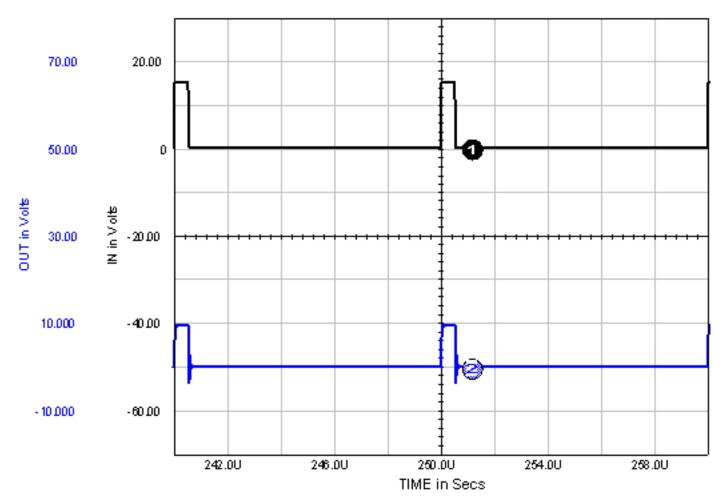

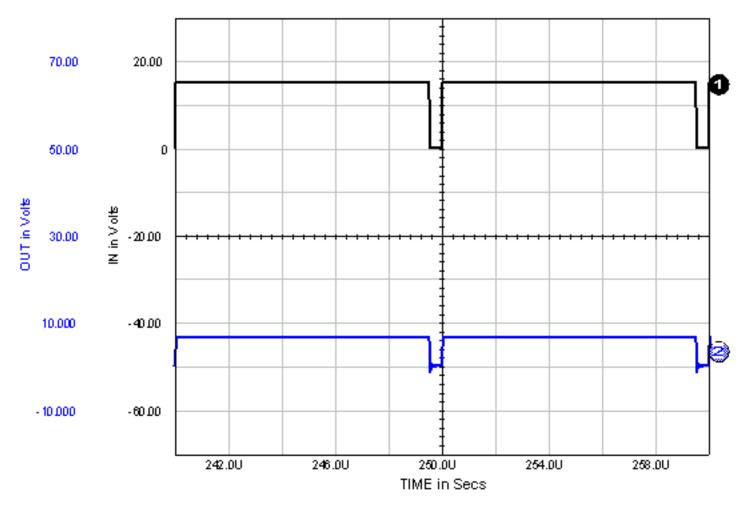

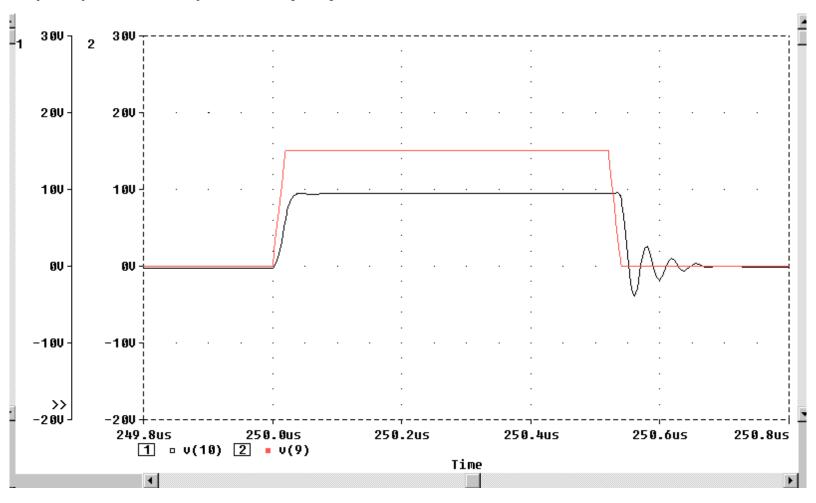

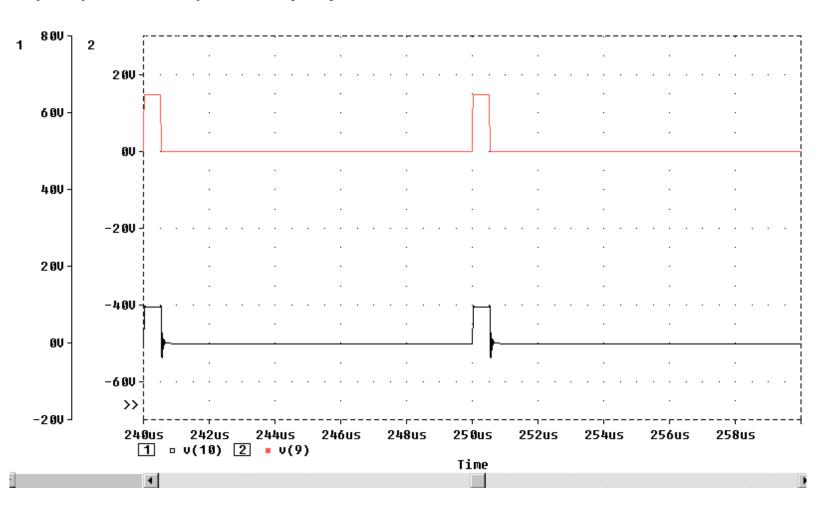

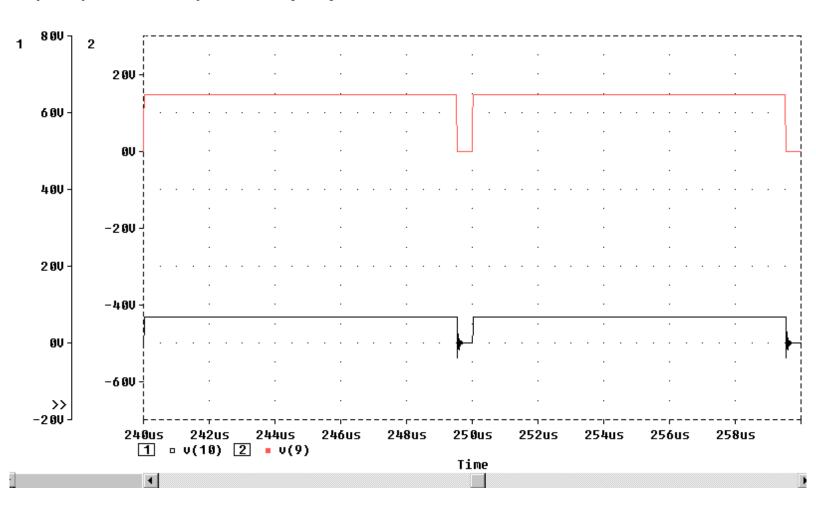

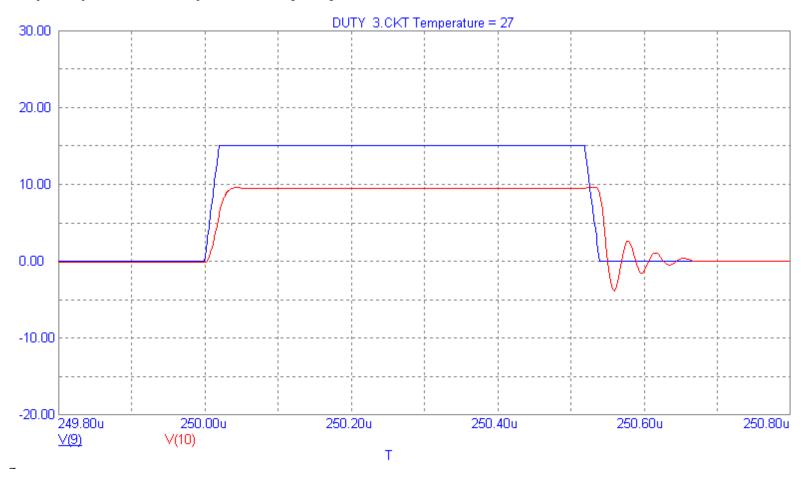

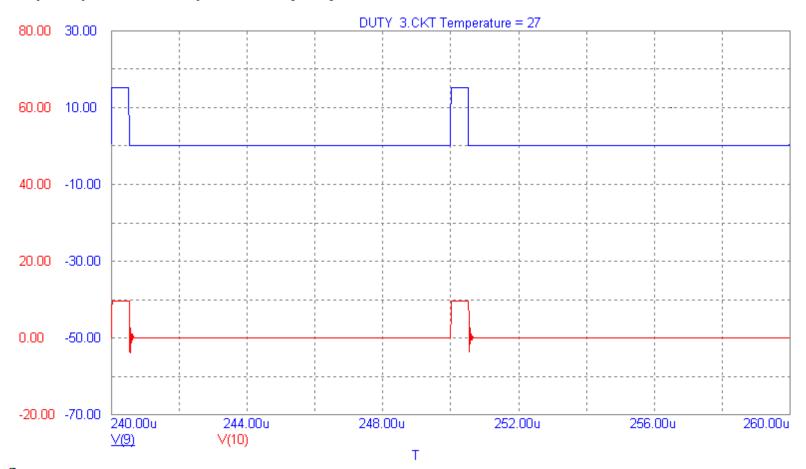

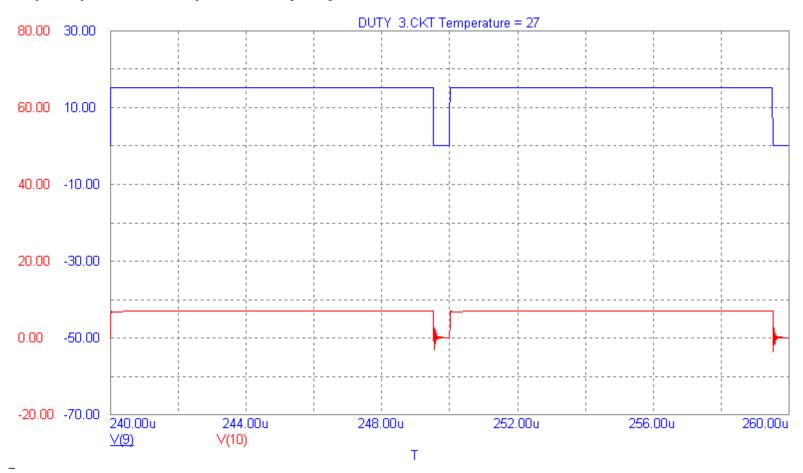

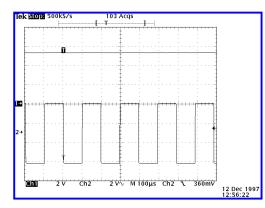

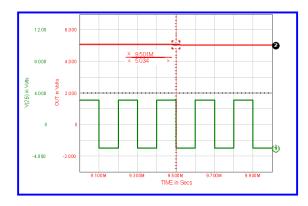

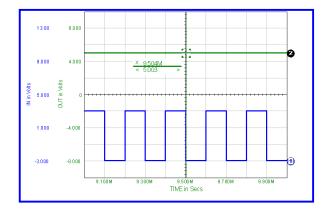

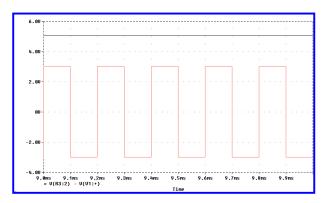

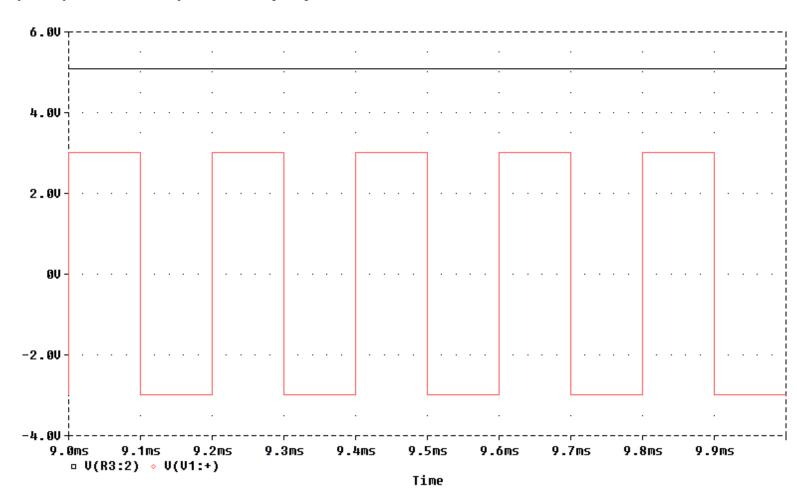

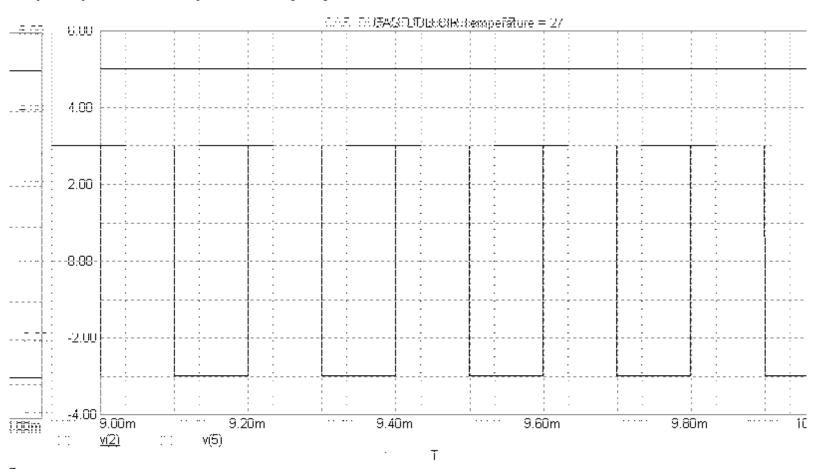

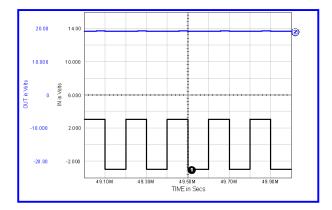

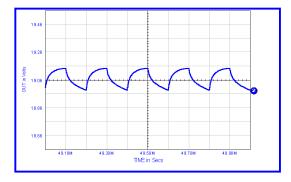

The parameters that will be measured in each of the software packages and the hardware are the minimum and maximum voltages, the rise and fall time of the output, and the effective pulse width. The results of the IsSpice model is shown as figure 5-2. Micro-cap V results are shown as figure 5-3. The Pspice results are displayed as figure 5-4, and the hardware measurements are shown as figure 5-5.

Bessel-Thompson Delay low pass filter with pulse shaper

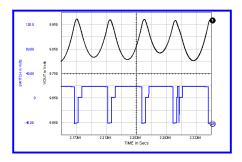

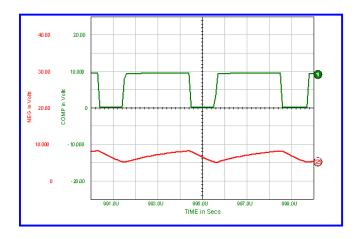

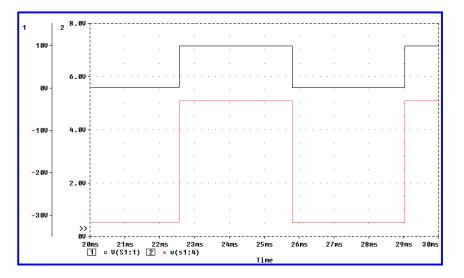

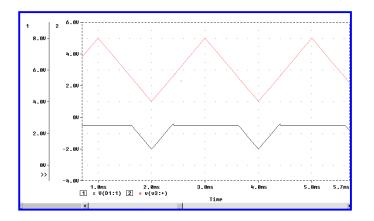

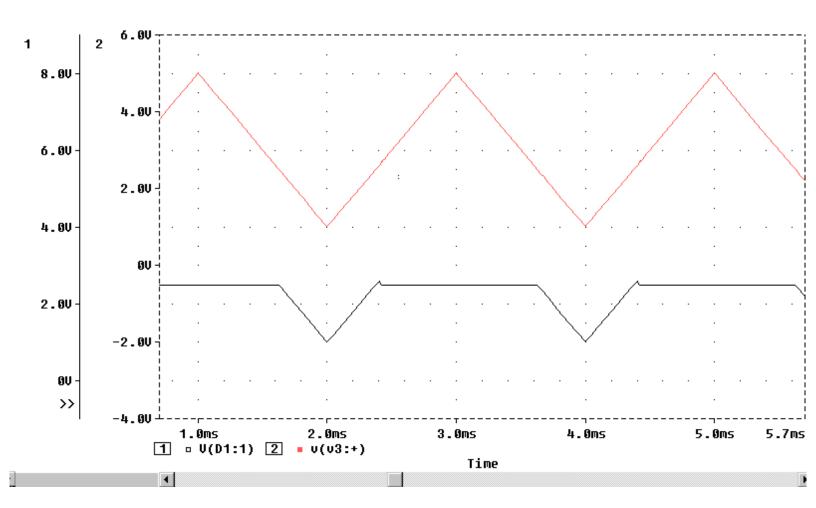

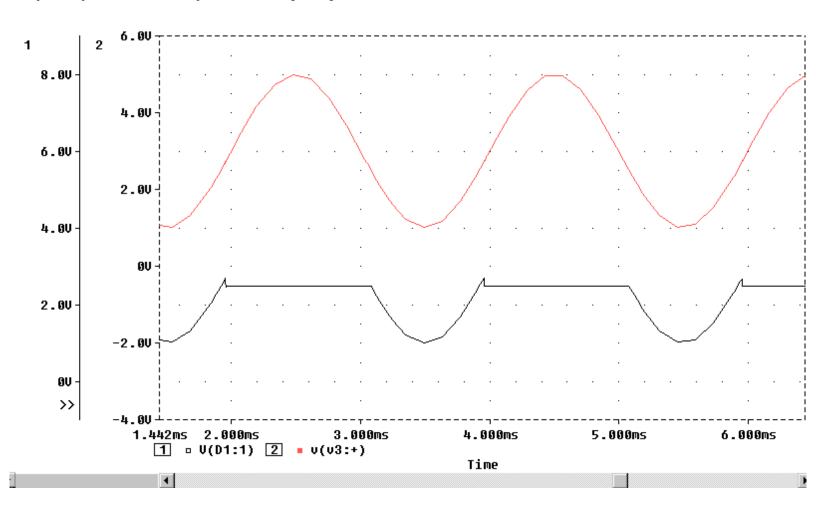

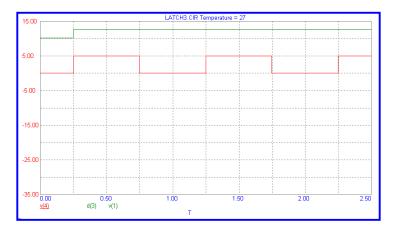

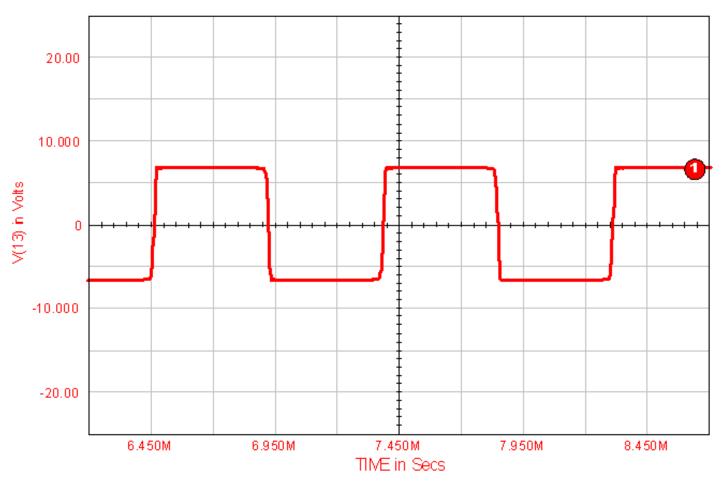

Figure 5-2: IsSpice simulation results

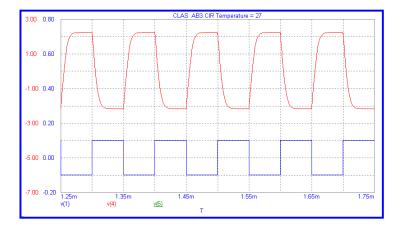

Note: Outmax=8.4, Outmin=-10.7, Rise time=53.3u, fall time=53.3u, pulse width=890u

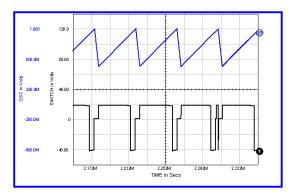

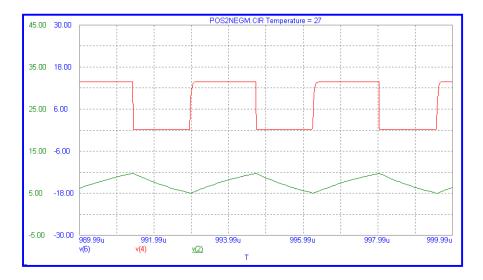

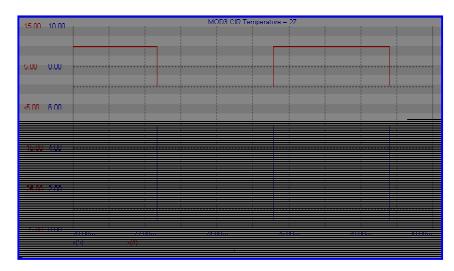

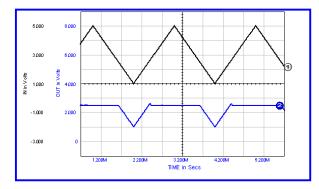

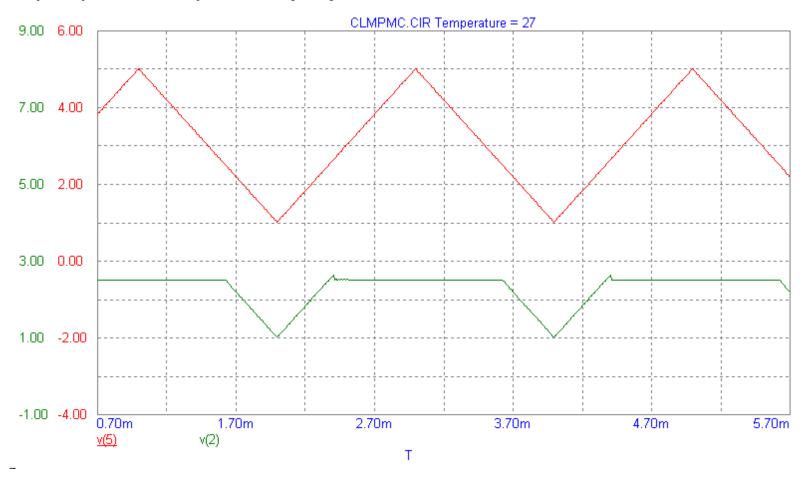

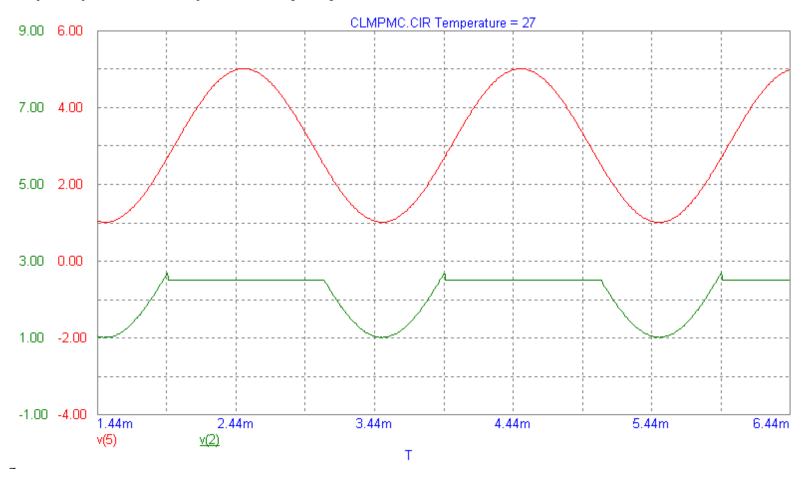

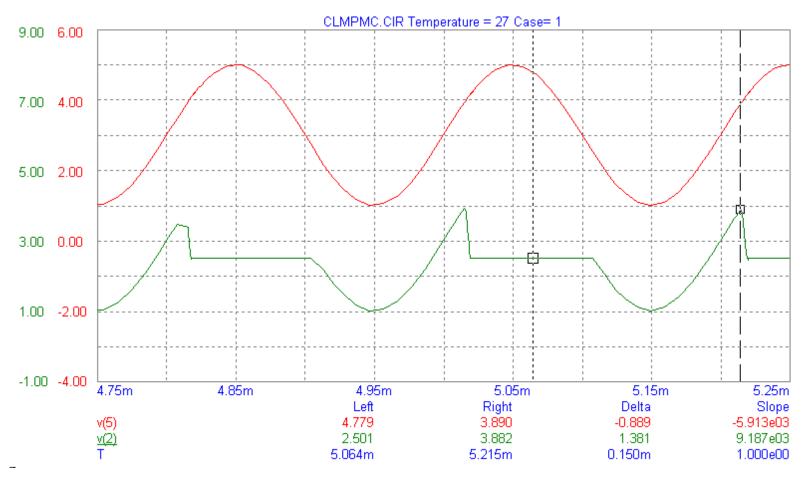

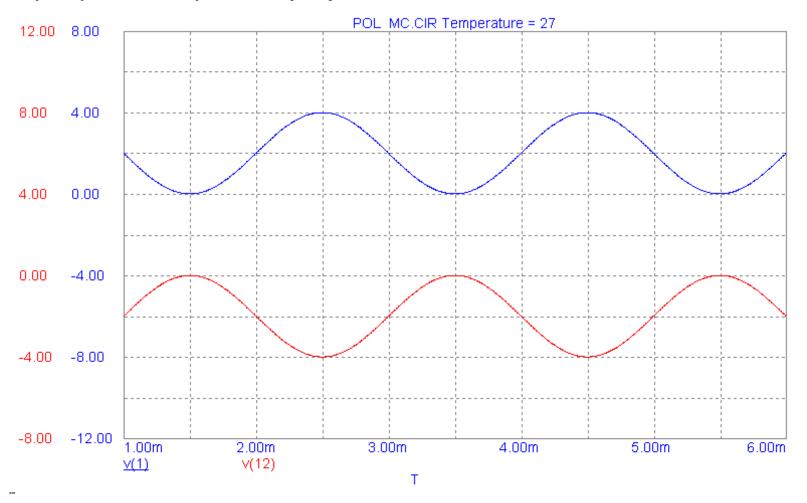

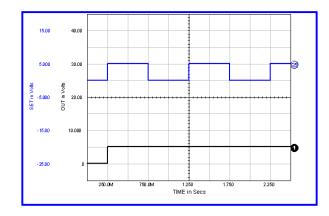

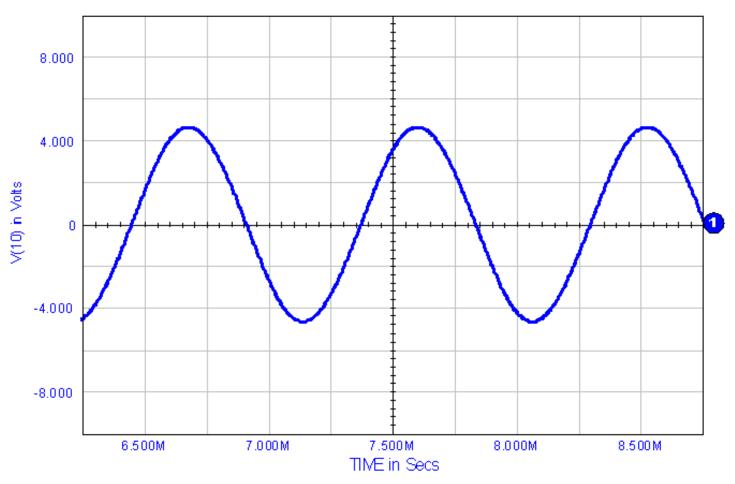

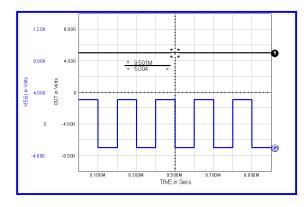

Figure 5-3: Microcap simulation results

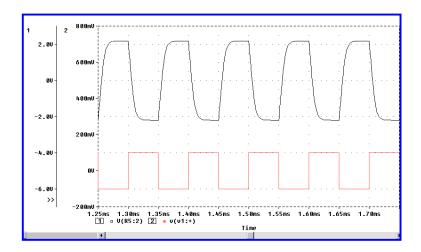

Note: Outmax=7.4, Outmin=-10.7, Rise time=49u, fall time=52u, pulse width=833u:

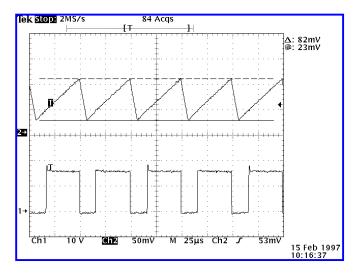

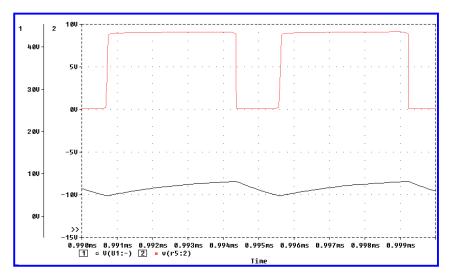

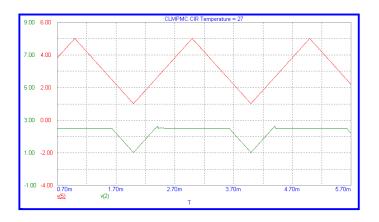

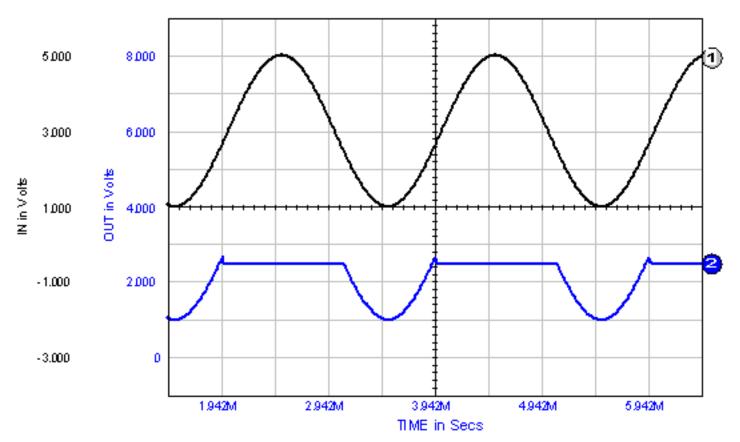

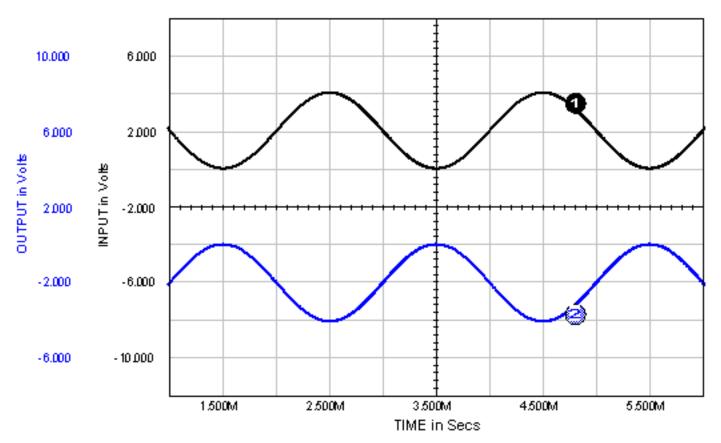

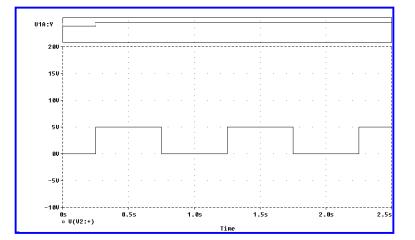

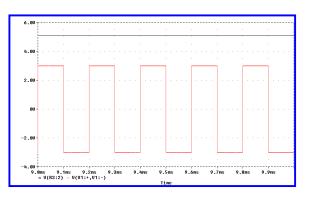

Figure 5-4: Pspice simulation results

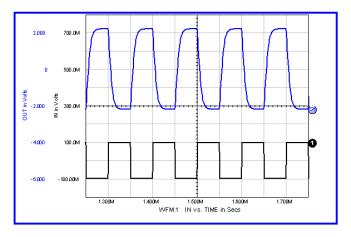

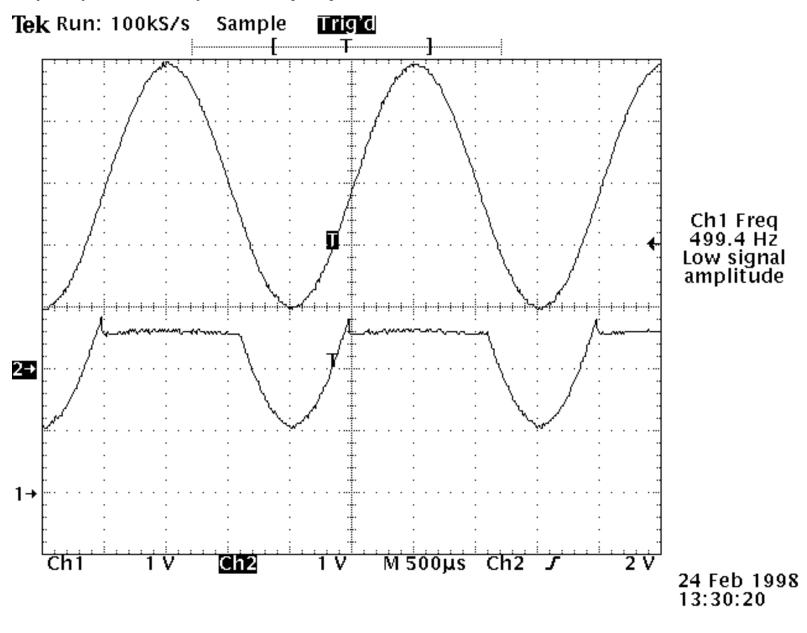

Note: Outmax=9.08, Outmin=-10.47, Rise time=84u, fall time=71u, pulse width=851u:

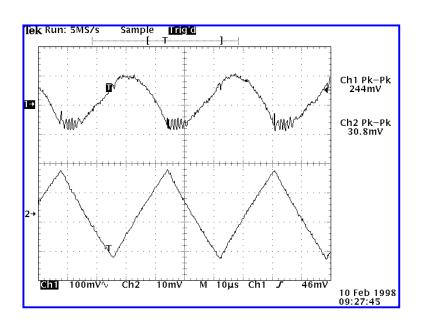

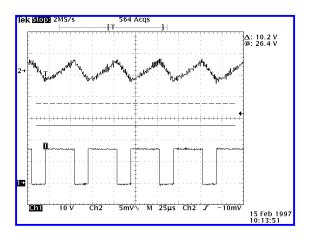

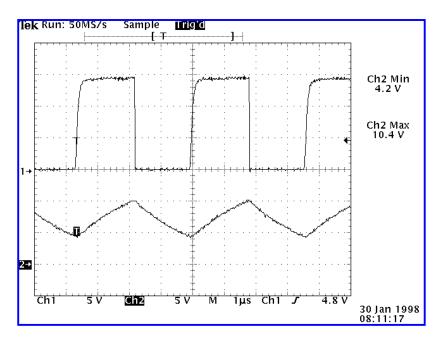

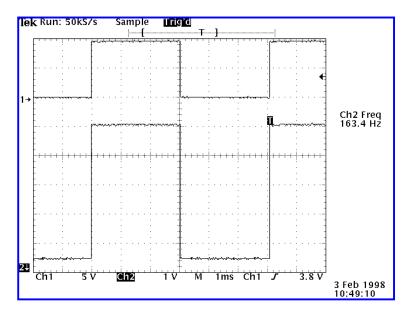

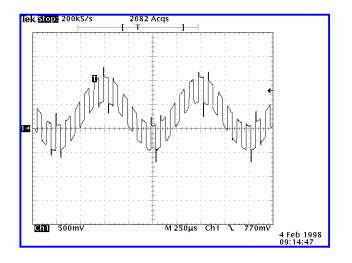

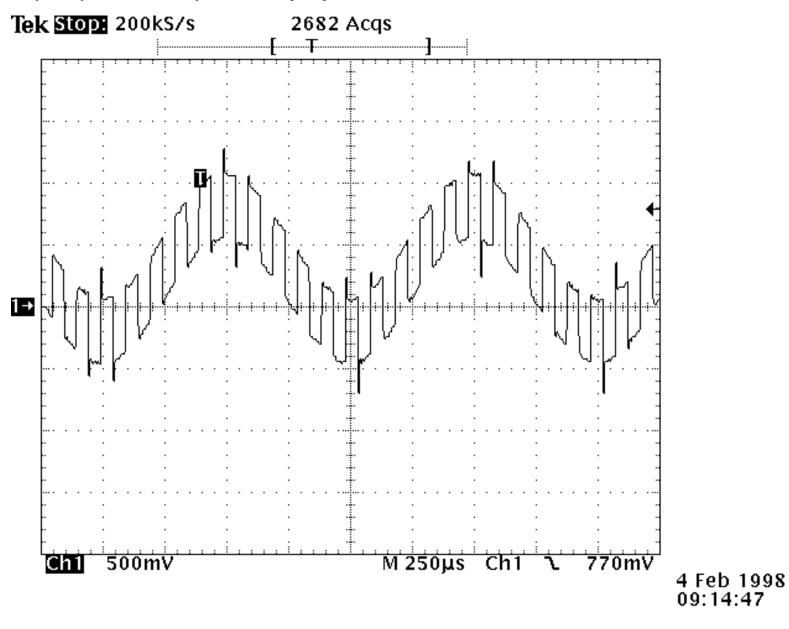

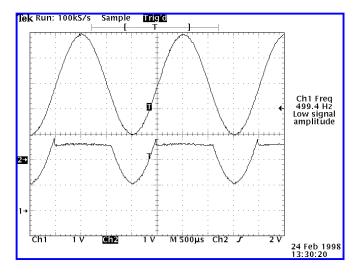

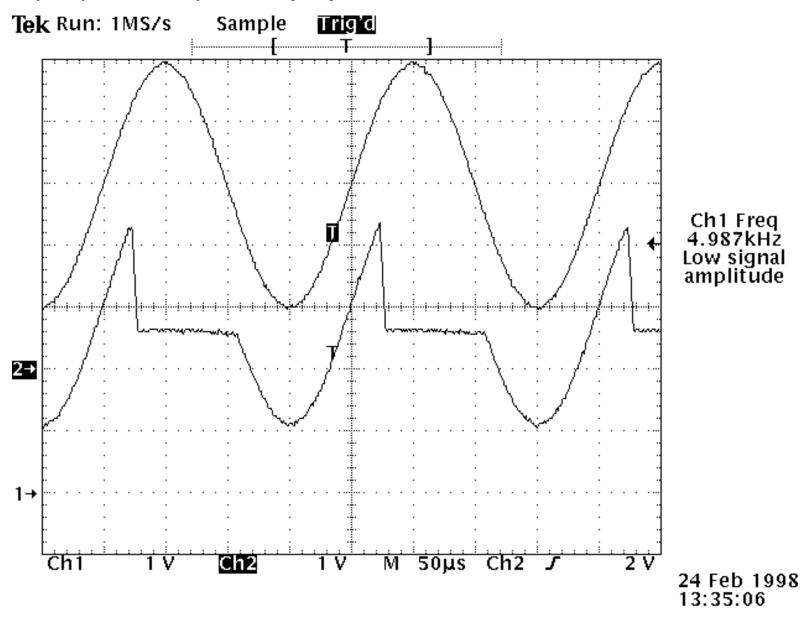

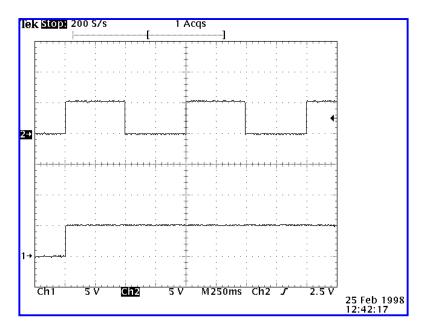

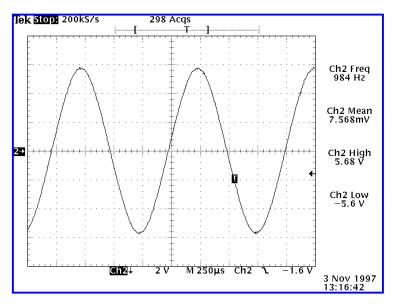

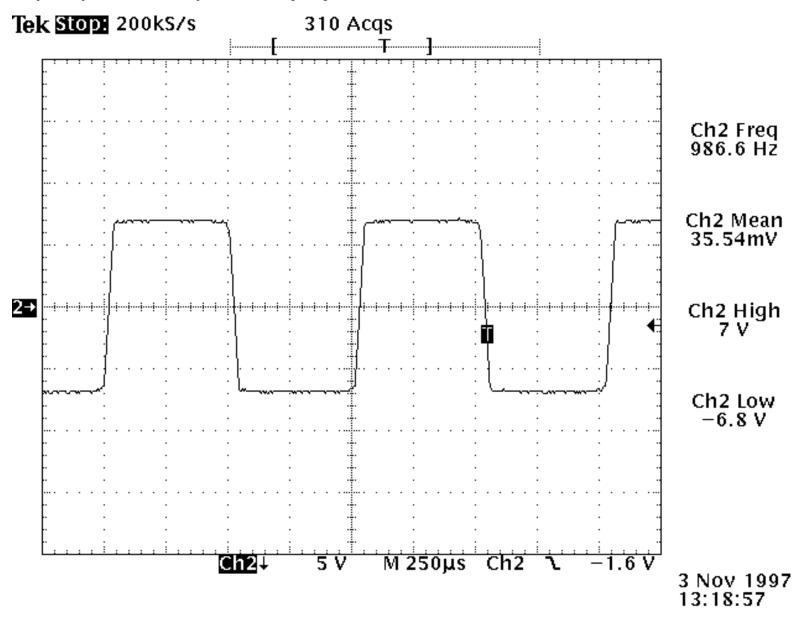

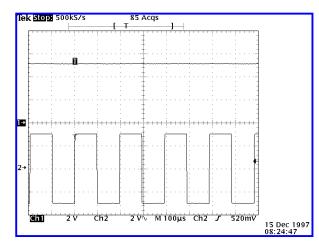

Figure 5-5: Breadboard data

Note: Outmax=9.1, Outmin=-10, Rise time=49u, fall time=50u, pulse width=780u:

| Run Time Summary                                                                                                                                                             |              |                |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|--|--|

| IsSpice v 7.6                                                                                                                                                                | PsPice v 6.3 | Micro-Cap V v2 |  |  |

| 38.6 Sec                                                                                                                                                                     | 2.05 Sec     | 67.4 Sec       |  |  |

| Advantages: Moderate part count pulse delay and reshaper<br>Disadvantages: May require additional voltage source and opamp package to<br>reshape voltage to a specification. |              |                |  |  |

Filenames: bessel (IsSpice) bes\_mic5 (Micro-cap) bes\_ps (Pspice)

Copyright 2002, PCBCafe. 1-888-44-WEB-44 http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image770.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image772.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image776.gif

## http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image777.gif

Inverted Bessel-Thompson Delay High pass filter

b: Inverted Bessel-Thompson Delay High pass filter

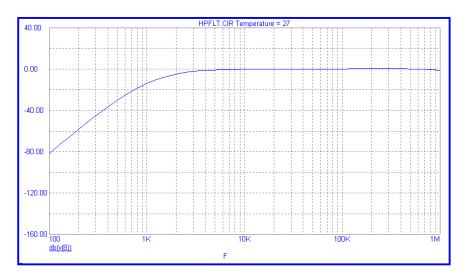

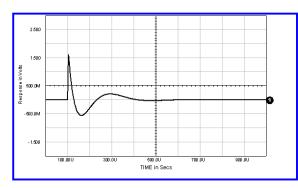

A quick modification to the Bessel-Thompson filter leaves us with a high pass filter. This filter does not have the built in delay like the low pass version, but it does provide an interesting response. The schematic and the breadboard results are shown in figure 6-1 and figure 6-2 respectively. The measurements that will be made for comparison purposes are the step response height and the time until the second cross of the zero axis.

Figure 6-1: High pass filter inverse Bessel-Thompson

Figure 6-2: Breadboard results of step response

For each filter an AC analysis was run for comparison between the different software packages. These results are displayed along with the step response from each of the filters for comparison between the software packages. The results of the IsSpice model are displayed as figure 6-3 and figure 6-4. The Pspice results are shown as figure 6-5 and figure 6-6. The results from the Microcap model are shown as figure 6-7 and figure 6-8.

request a free CD today >

Expedition<sup>™</sup> Series

Inverted Bessel-Thompson Delay High pass filter

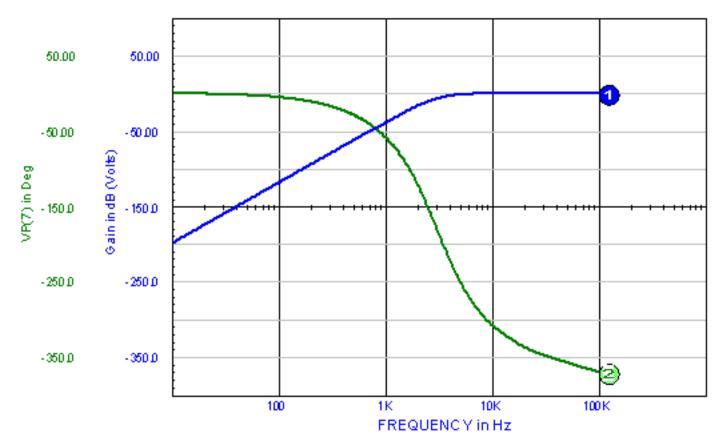

Figure 6-3: IsSpice results of step response

Figure 6-4: IsSpice AC filter response

Figure 6-5: Pspice results of step response

Figure 6-6: Pspice AC filter response

Figure 6-7: Microcap results of step response

Figure 6-8: Microcap AC filter response

| Run Time Summary                      |                             |          |  |  |

|---------------------------------------|-----------------------------|----------|--|--|

| IsSpice v 7.6                         | PsPice v 6.3 Micro-Cap V v2 |          |  |  |

| 2.25 Sec                              | 1.01 Sec                    | 18.8 Sec |  |  |

|                                       |                             |          |  |  |

| Advantages: Moderate parts count      |                             |          |  |  |

| Disadvantages: Under damped response. |                             |          |  |  |

Filenames: hpbessel (IsSpice) bes\_mic5 (Micro-cap) bes\_ps (Pspice)

# References

Inverted Bessel-Thompson Delay High pass filter

Parker, Sybil, ed. 1984. Concise Encyclopedia of Science and Technology. New York: McGraw Hill

Van Valkenburg, M.E. 1982. Analog Filter Design. New York: Harcort Brace Jovanovich College Publishers.

> Copyright 2002, PCBCafe. 1-888-44-WEB-44

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image778.gif

#### http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image780.gif

$$q_c := \frac{\omega_0}{\omega_2 - \omega_1}$$

$$\Omega_s := \frac{\omega_4 - \omega_3}{\omega_2 - \omega_1}$$

$$\Omega_{\mathbf{p}} := -\left[\frac{-\left(\omega_2^2\right) + \omega_0^2}{\omega_2 \cdot \left(\omega_2 - \omega_1\right)}\right]$$

$$\alpha_{\max} := 10 \frac{\ln \left[ \frac{\left[ \cosh \left( n \cdot \operatorname{acosh} \left( \frac{\Omega_s}{\Omega_p} \right) \right)^2 + 10^{\left( \frac{1}{10} \cdot \alpha_{\min} \right)} - 1 \right]}{\cosh \left( n \cdot \operatorname{acosh} \left( \frac{\Omega_s}{\Omega_p} \right) \right)^2} \right]}{\ln(10)}$$

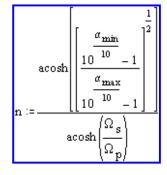

## n = 2.975

Round up to an interger.

ceil(n) = 3

http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-08.php (2 of 9) [19/01/2002 22:02:07]

| $\psi$ := | 180<br>2·n      | if $\frac{n}{2}$ = floor $\left(\frac{n}{2}\right)$ |

|-----------|-----------------|-----------------------------------------------------|

|           | <u>180</u><br>n | otherwise                                           |

ψ = 60

$$\psi := \psi \cdot \frac{\pi}{180}$$

$$\varepsilon := \left(\frac{\alpha_{\max}}{10^{-10}} - 1\right)^{\frac{1}{2}}$$

The pole locations are now determined:

$$a := \frac{1}{n} \cdot \operatorname{asinh}\left(\frac{1}{\varepsilon}\right)$$

**Real Poles:**

For  $\psi = 0$ ; n odd

$$\sigma_{s} \coloneqq |\sinh(a)|$$

**Complex Poles:**

For  $\psi = (\psi, +/-2\psi, +/-3\psi....)$

$\sigma_{\mathbf{k}} \coloneqq | \cdot \sinh(\mathbf{a}) \cdot \cos(\psi) |$

$$\omega_{\mathbf{k}} \coloneqq |\operatorname{cosh}(\mathbf{a}) \cdot \sin(\psi)|$$

The half power (3-dB) frequency is determined by:

$$G := \sqrt{E^2 - 4 D^2}$$

$$Q := \frac{1}{D} \cdot \sqrt{\frac{1}{2} \cdot (E + G)}$$

$$K := \frac{\Sigma \cdot Q}{q_c}$$

$W := K + \sqrt{K^2 - 1}$

$$\omega_{01} := \frac{1}{W} \cdot \omega_0$$

Set all values of capacitors to be equal

$$C := 10^{-7}$$

$$K_{m1} := \frac{1}{2 \cdot Q \cdot C \cdot \omega_{01}}$$

$$K_{m2} := \frac{1}{2 \cdot Q_0 \cdot C \cdot \omega_0}$$

$$K_{m3} := \frac{1}{2 \cdot Q \cdot C \cdot \omega_{02}}$$

Stage one:

$$\mathbb{R}_1 := (\mathbb{T}_1) \cdot \mathbb{K}_{m1}$$

Stage 2:

$$\mathbf{R}_{5} := \frac{1}{1 - \frac{1}{\mathbf{T}_{2}}} \cdot \mathbf{K}_{\mathbf{m}2}$$

$$R_6 := 4 \cdot Q_0^2 \cdot K_m^2$$

Stage 3:

$$\mathbb{R}_7 \coloneqq (\mathbb{T}_3) \cdot \mathbb{K}_m$$

$$R_8 := \frac{1}{1 - \frac{1}{T_3}} K_m 3$$

$$R_9 := 4 \cdot Q^2 \cdot K_{m2}$$

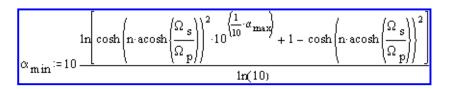

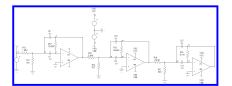

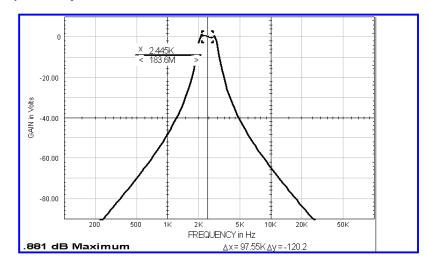

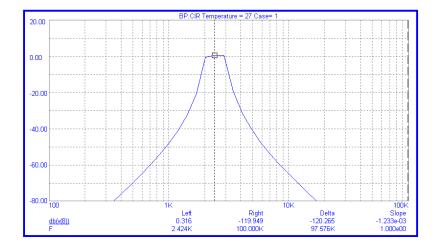

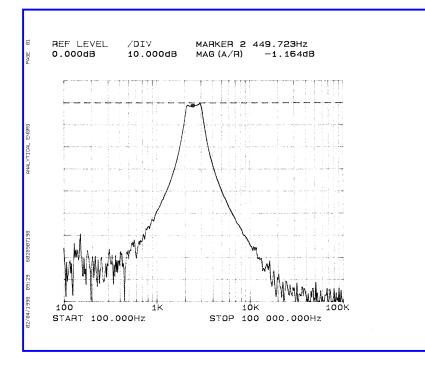

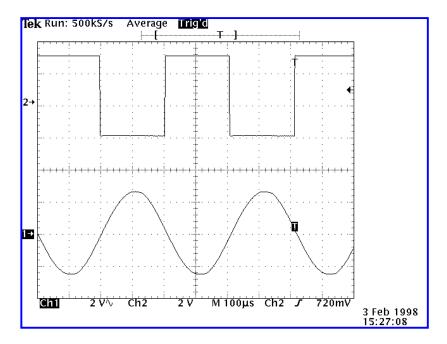

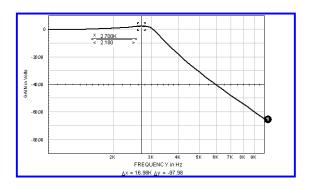

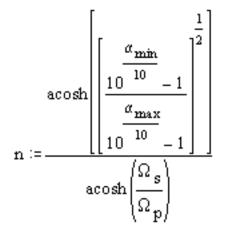

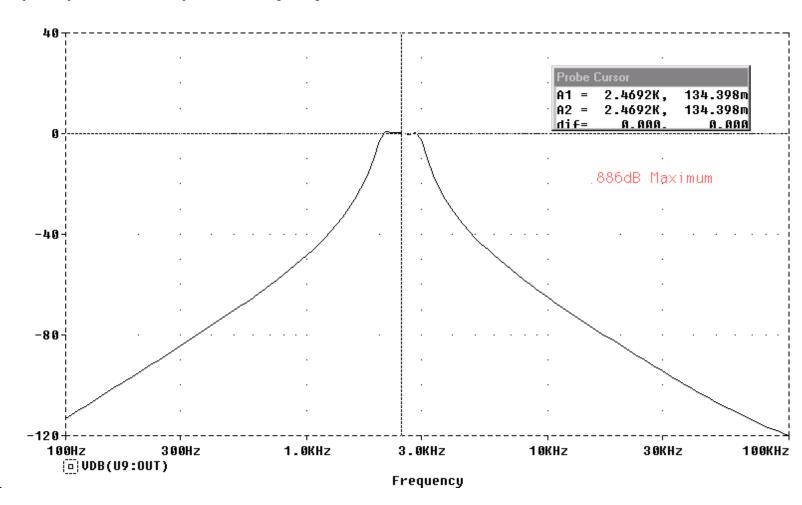

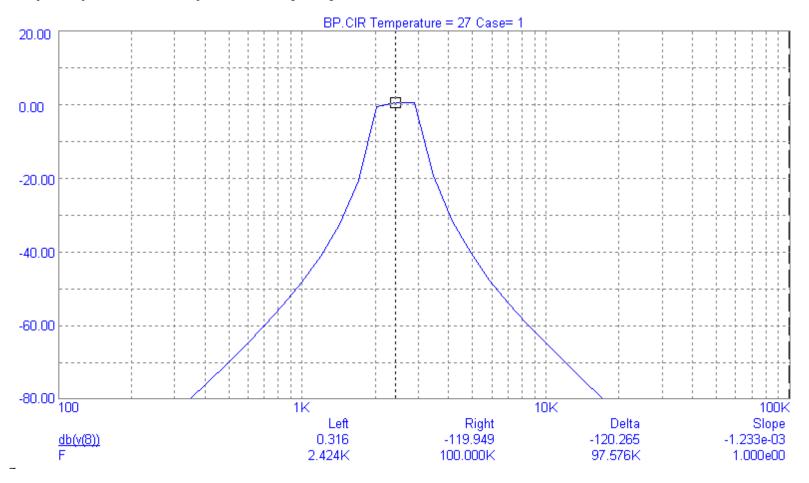

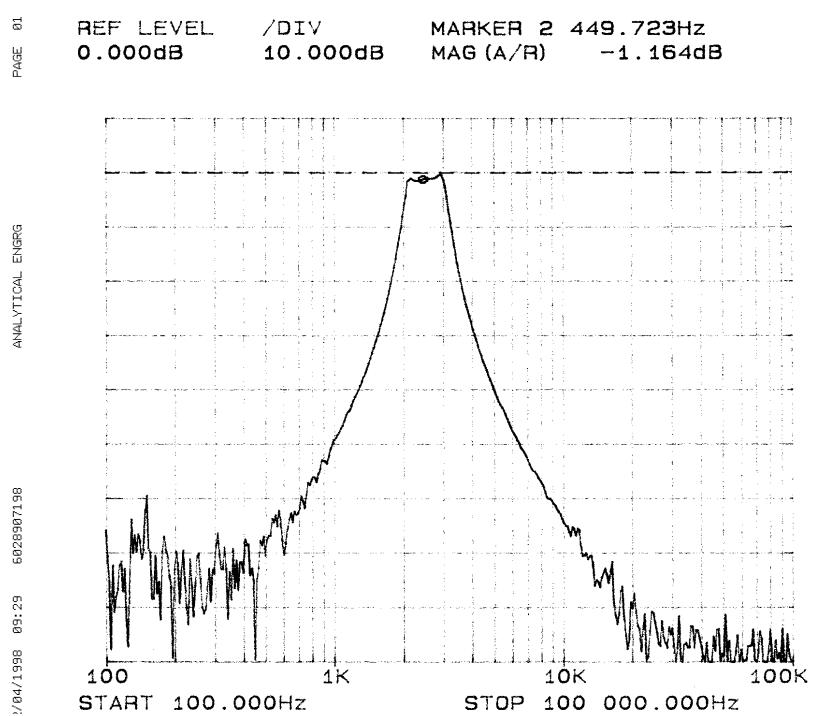

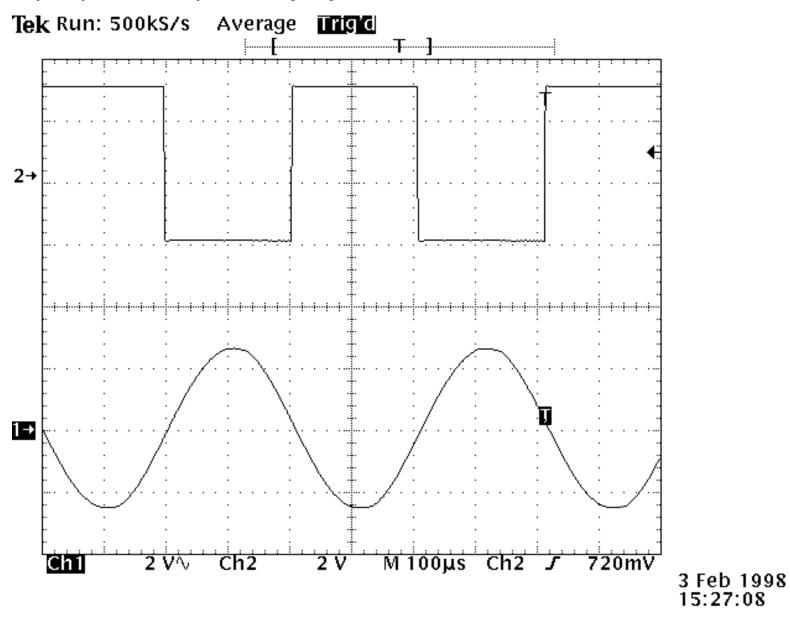

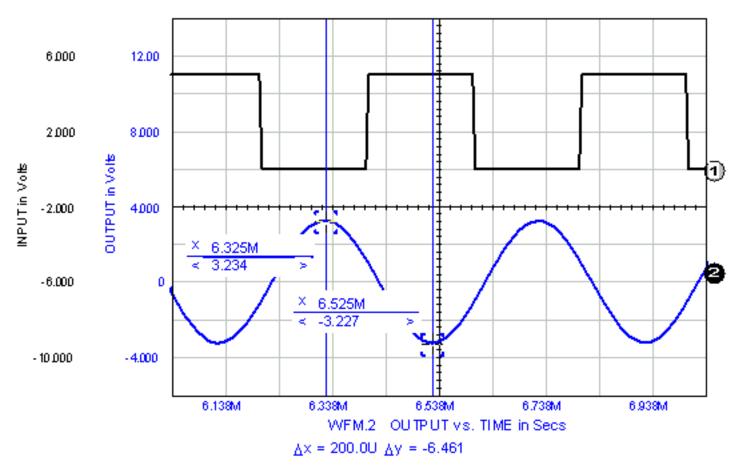

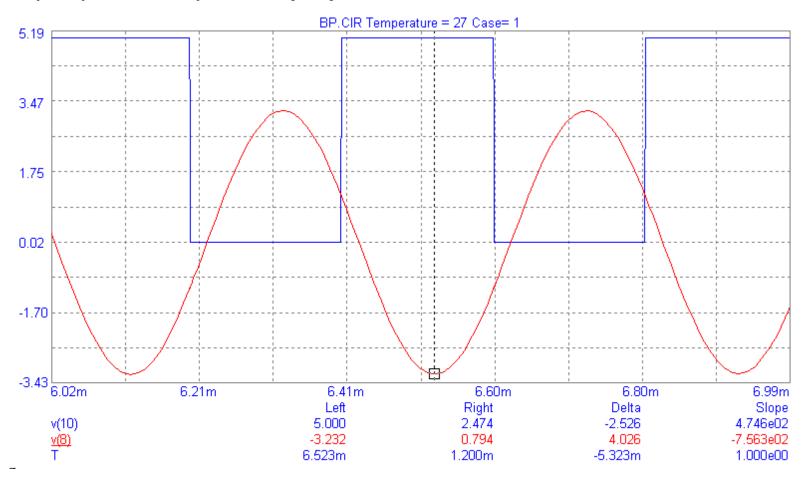

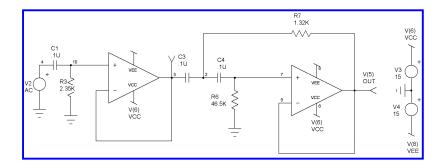

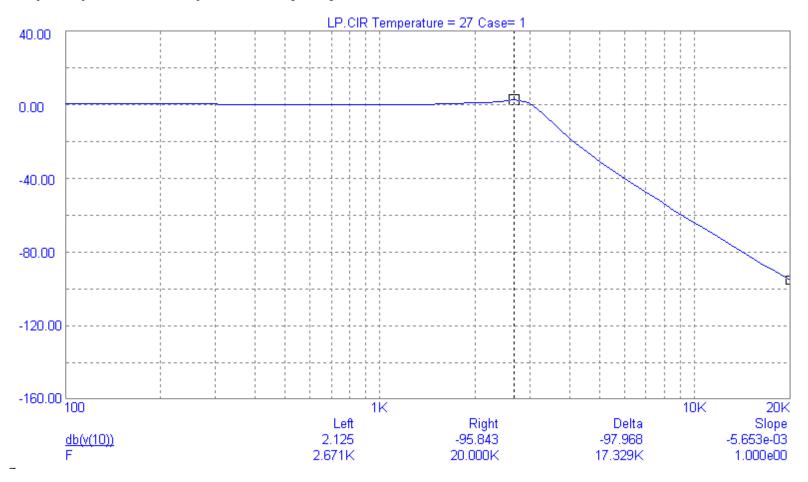

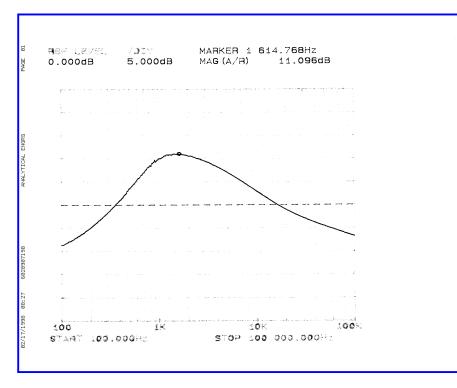

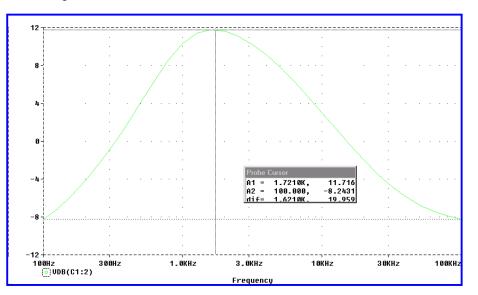

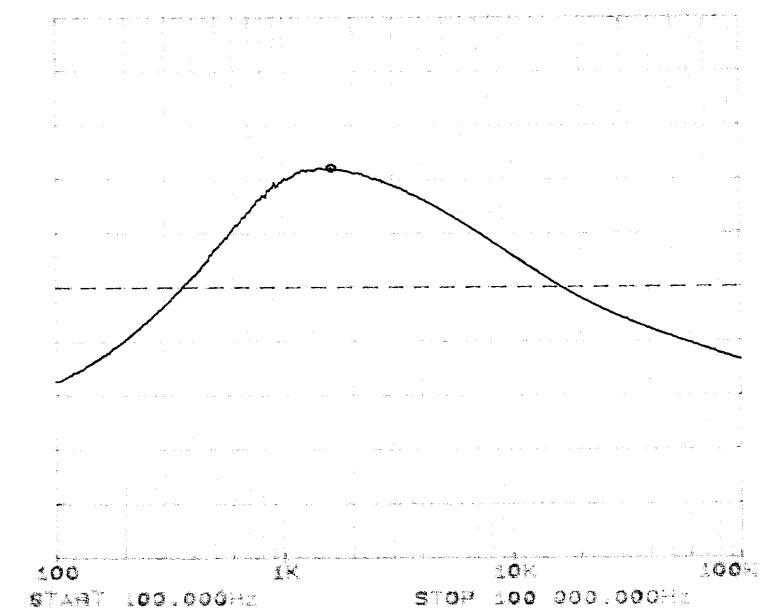

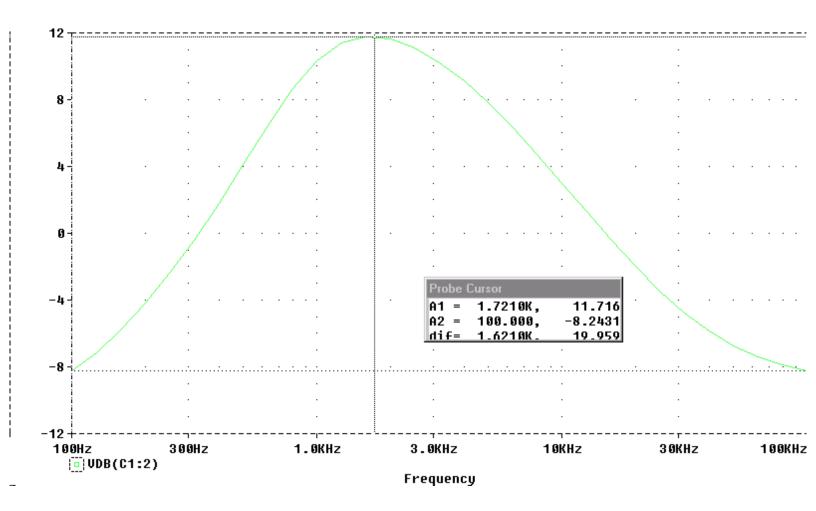

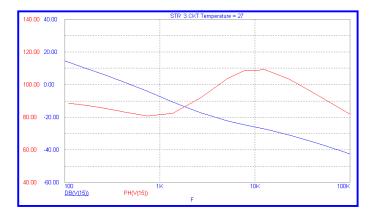

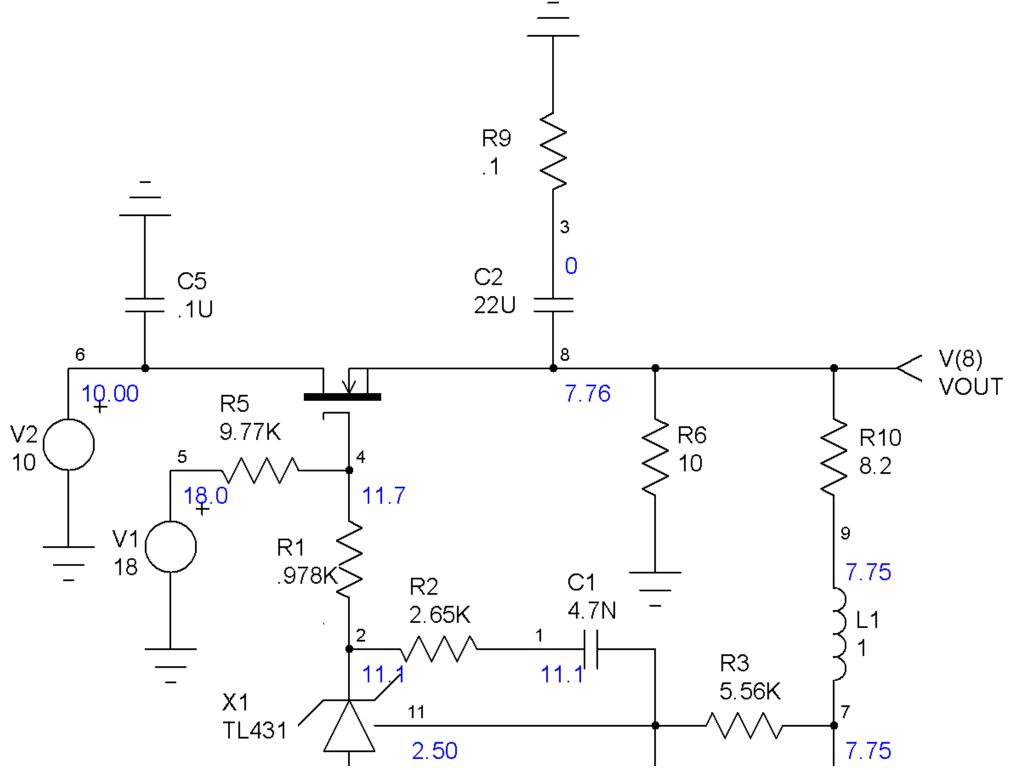

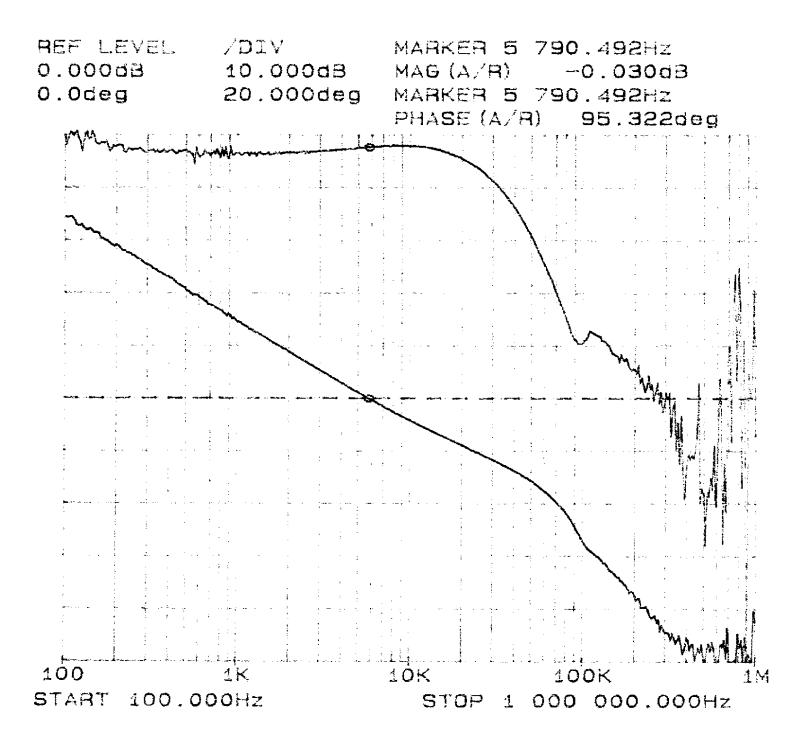

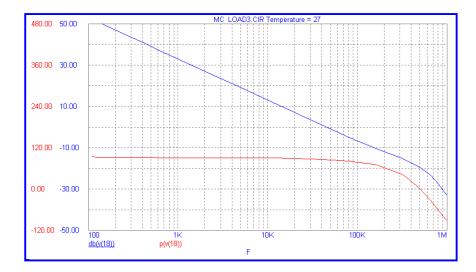

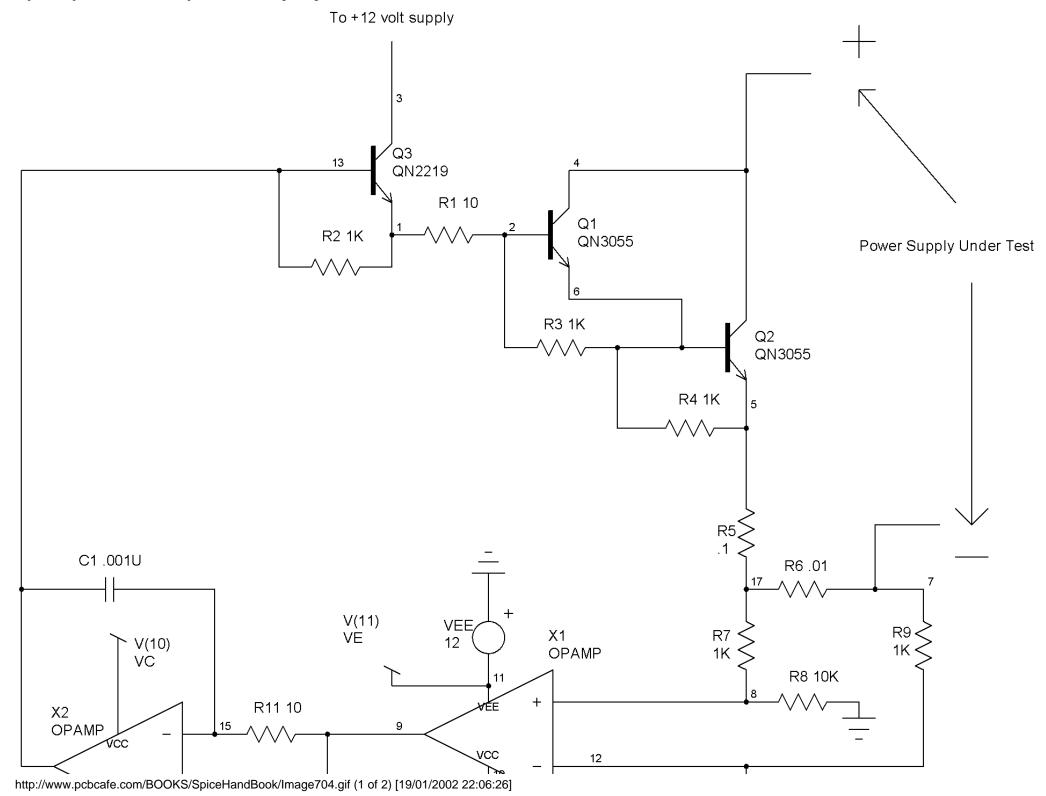

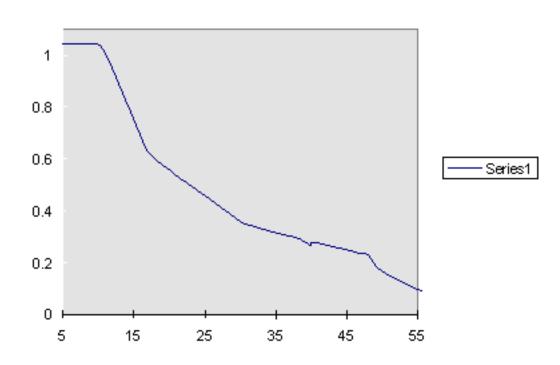

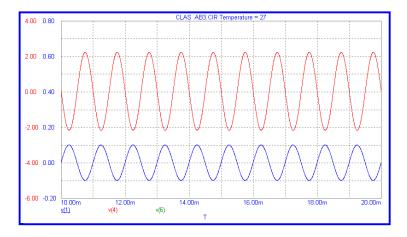

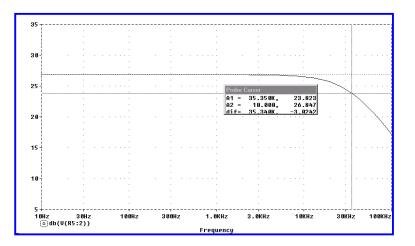

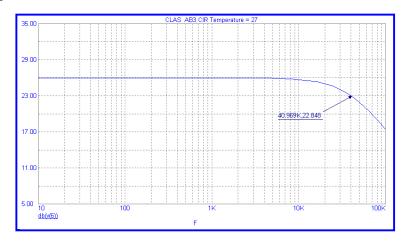

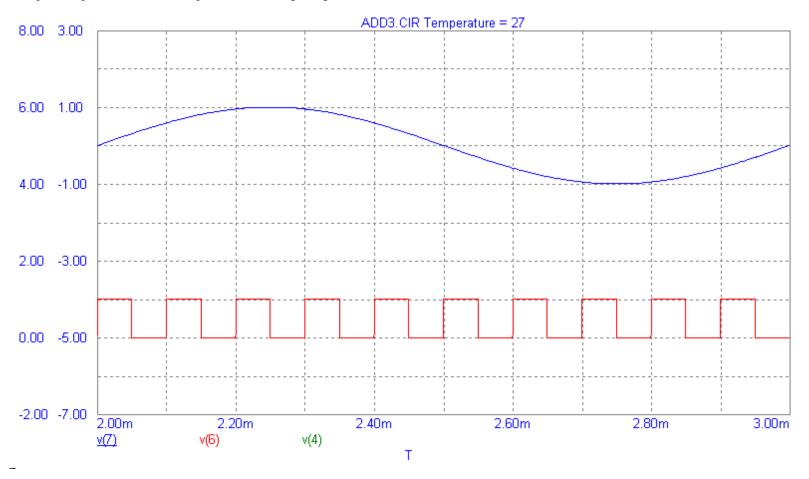

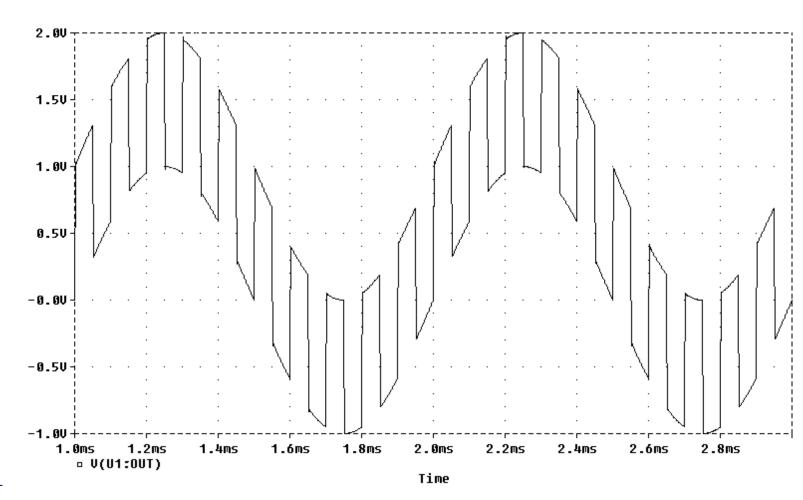

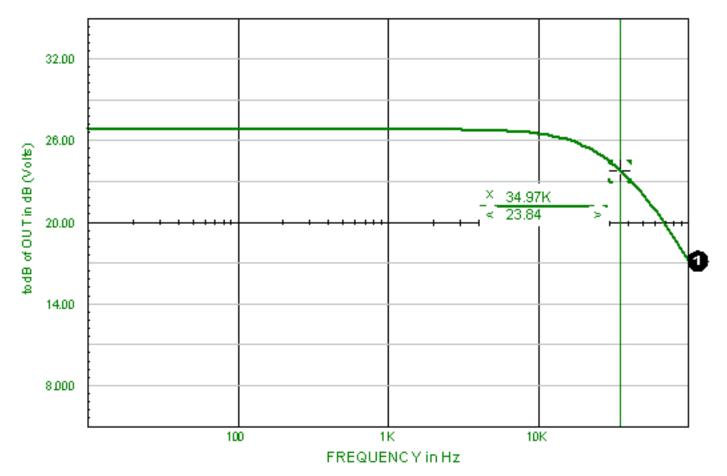

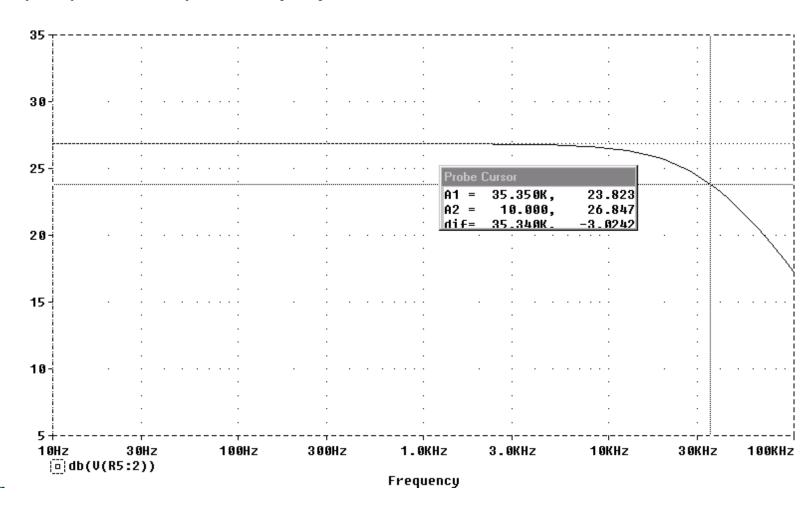

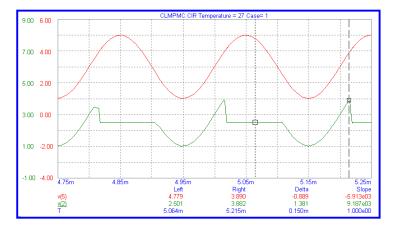

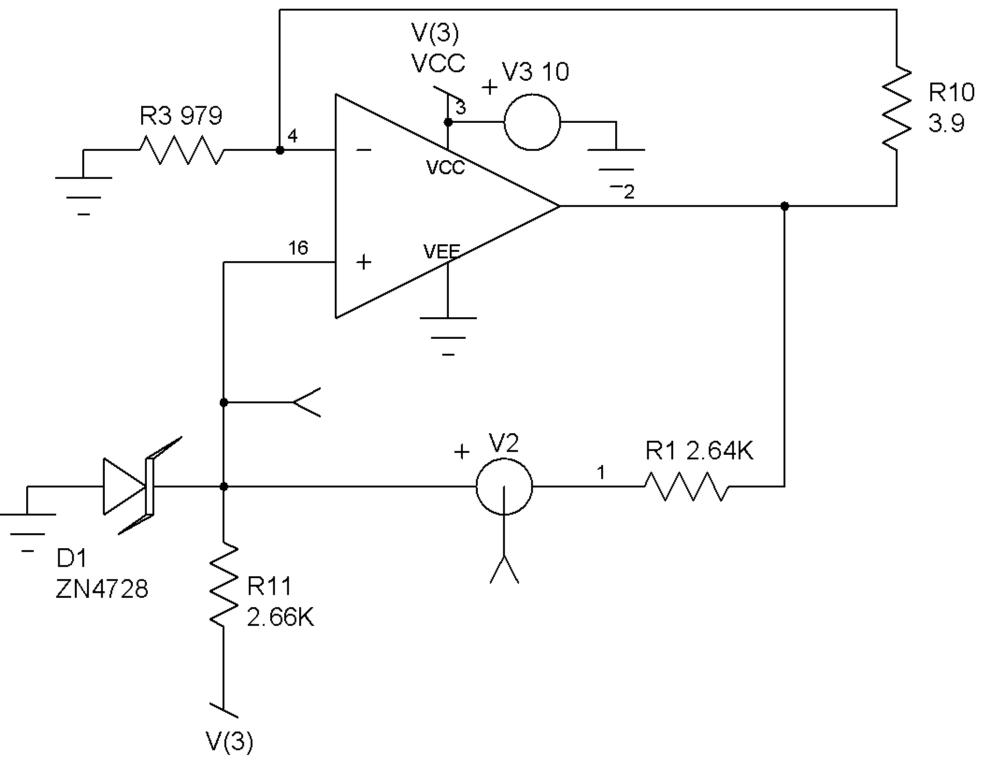

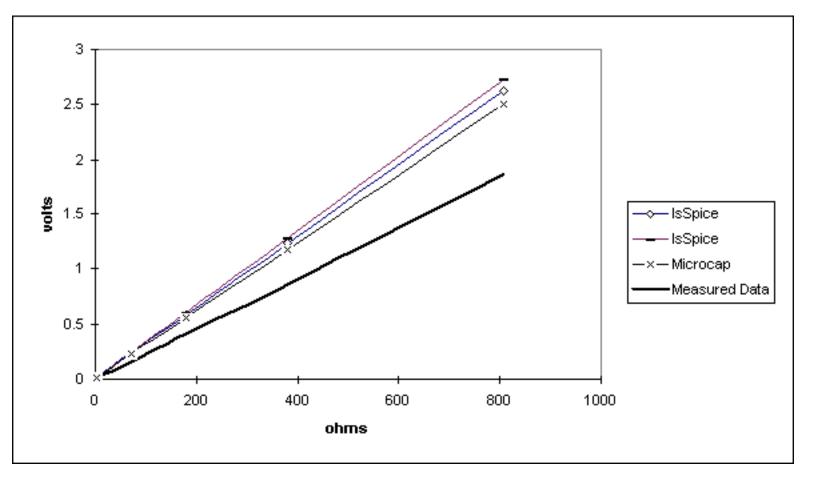

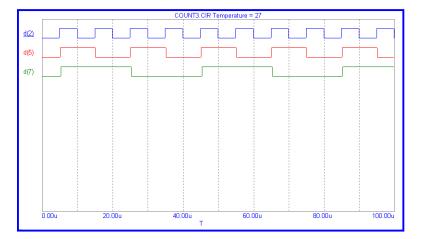

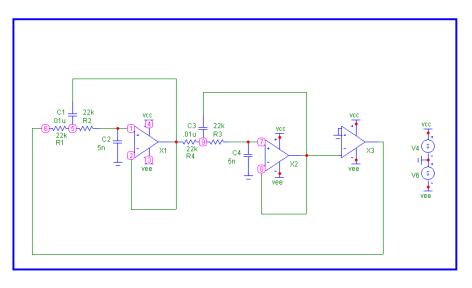

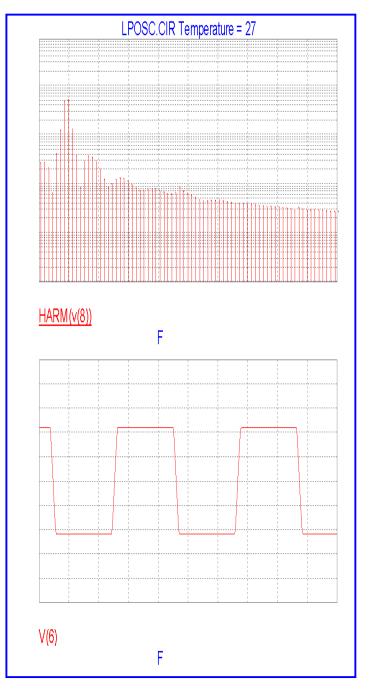

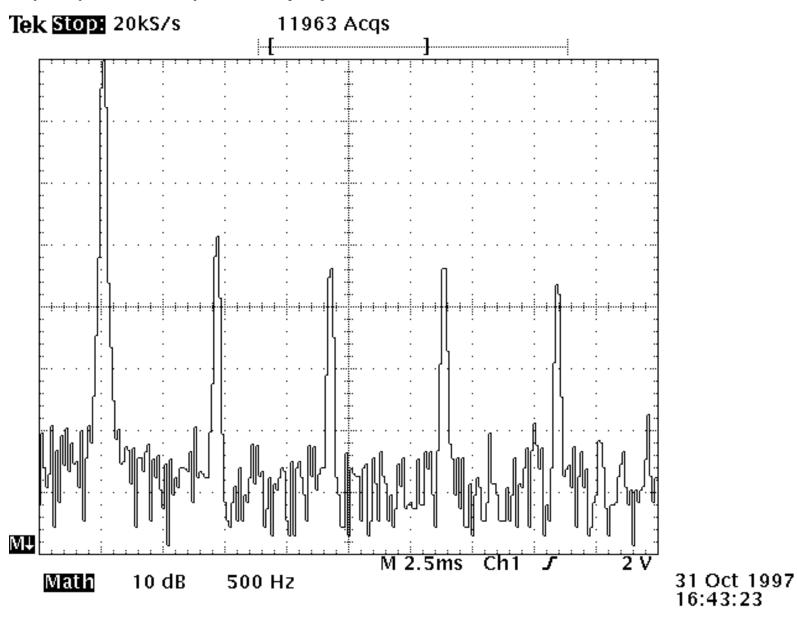

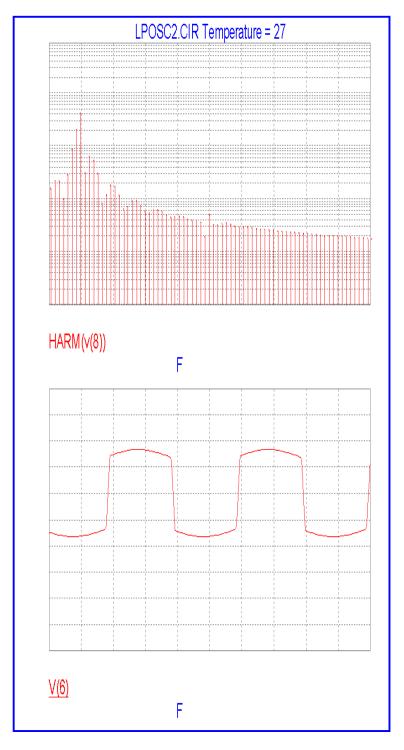

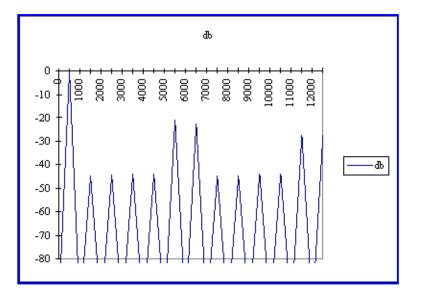

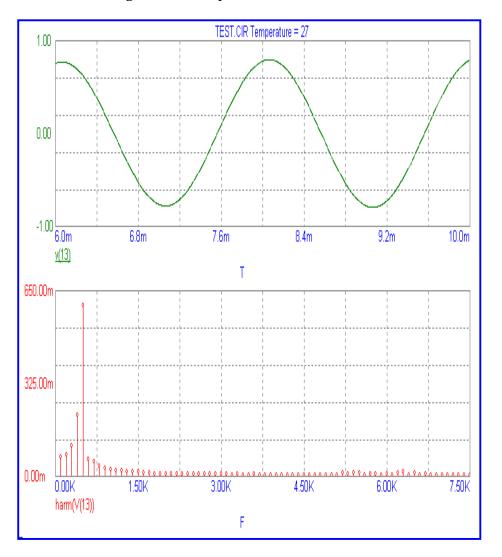

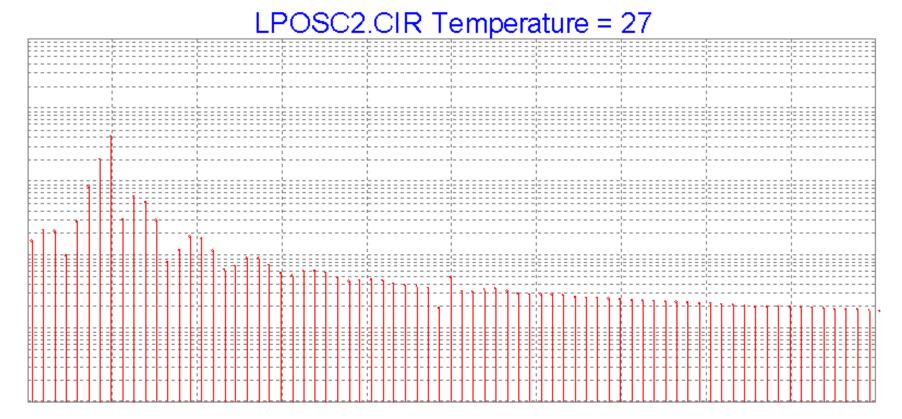

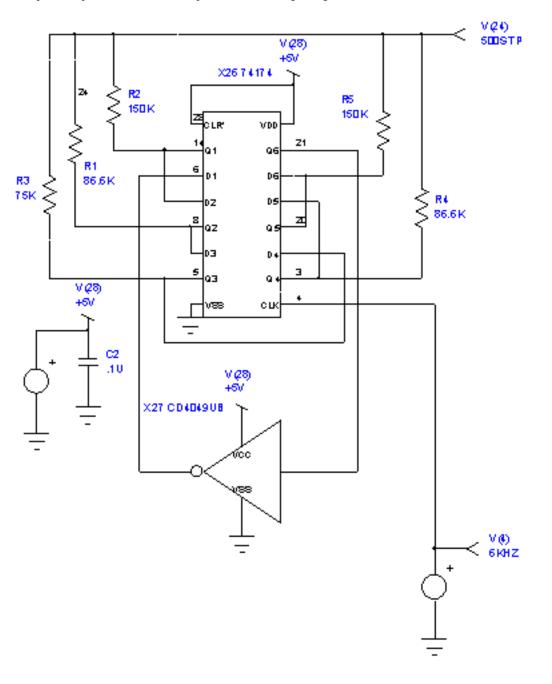

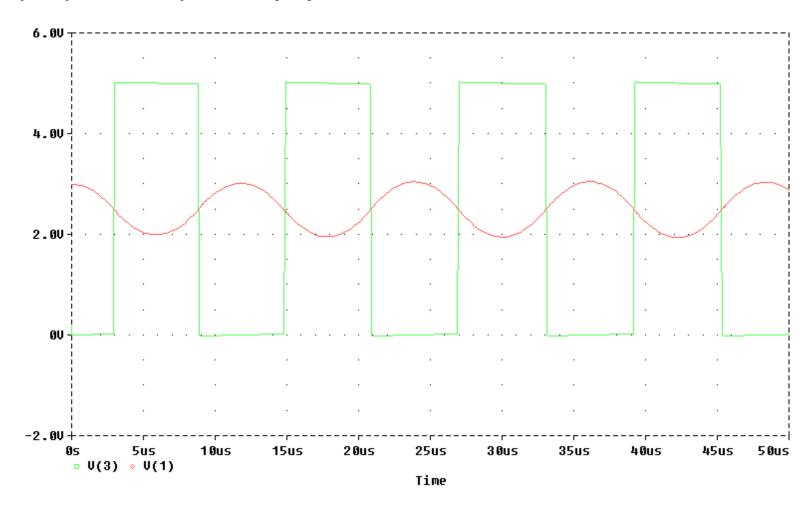

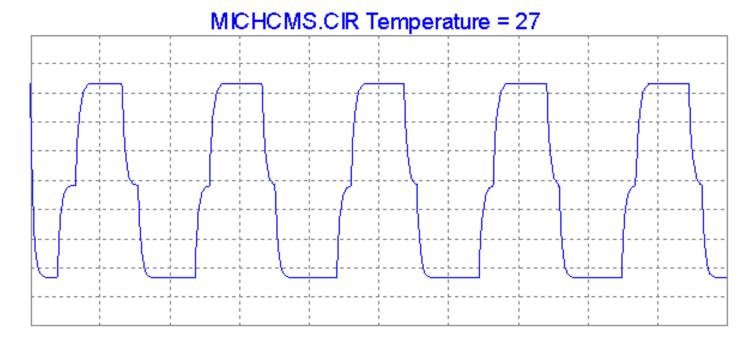

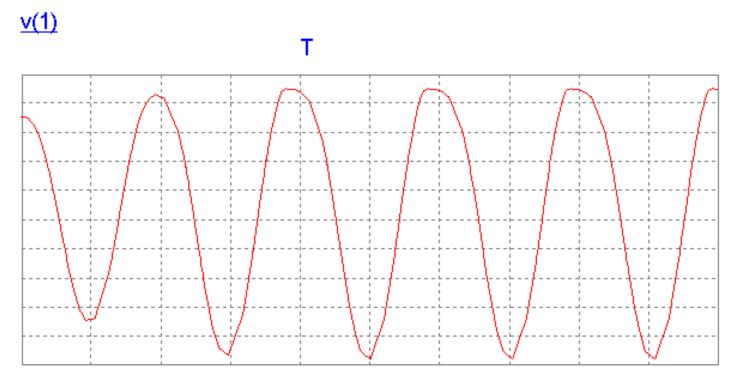

The schematic in Figure 7-1 of the Chebyshev bandpass filter utilized the predicted values from the mathcad file, where lab resources allowed. Close approximations were used, which the circuit performance was extremely sensitive to. Any deviations from the values predicted in the mathcad file resulted in gain in the passband. Using SPICE to test possible circuit realizations greatly reduces the time to implement hardware. SPICE will predict if a given circuit realization will perform as desired with available parts, before actual hardware measurements are made. This is helpful because Chebyshev circuit realization can be difficult, small changes in the circuit elements can result in undesired performance. The simulated AC results from Ispice, Pspice, and Micro-Cap V are shown in Figure 7-2 through Figure 7-4 respectively. The measured breadboard AC response of the filter is shown in Figure 7-5, and the measured transient response in shown Figure 7-8. All of the simulators correlated well to the hardware.

Figure 7-1: Chebyshev Bandpass Filter

Figure 7-2: Ispice Simulated Chebyshev Bandpass Filter Response

Figure 7-3: Pspice Simulated Chebyshev Bandpass Response

Figure 7-4: Micro-CapV Simulated Chebyshev Bandpass Response

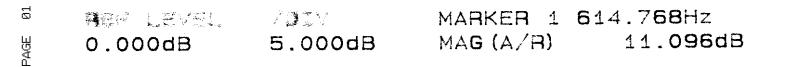

Figure 7-5: Measured Cebyshev Bandpass Filter Response

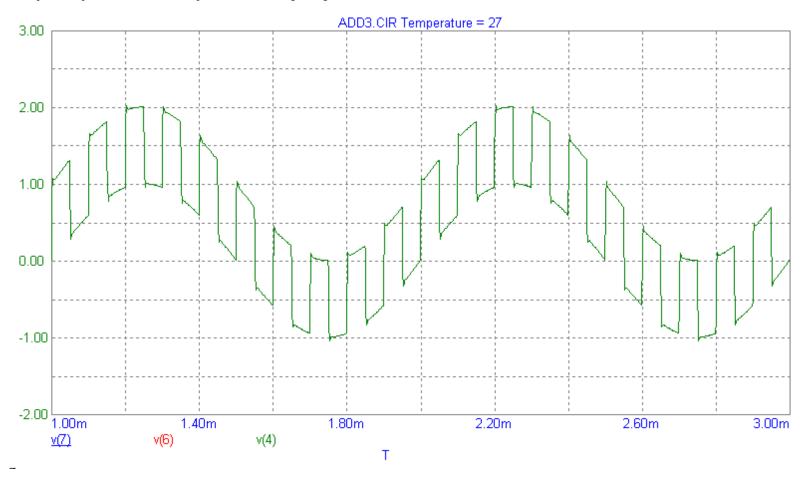

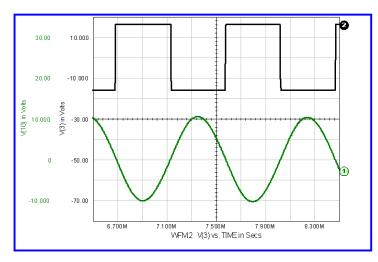

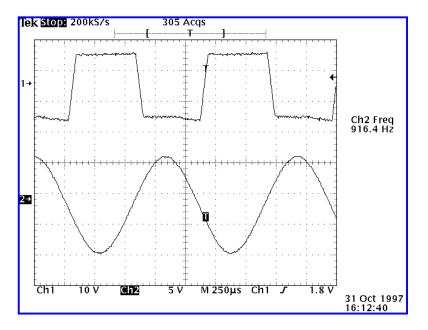

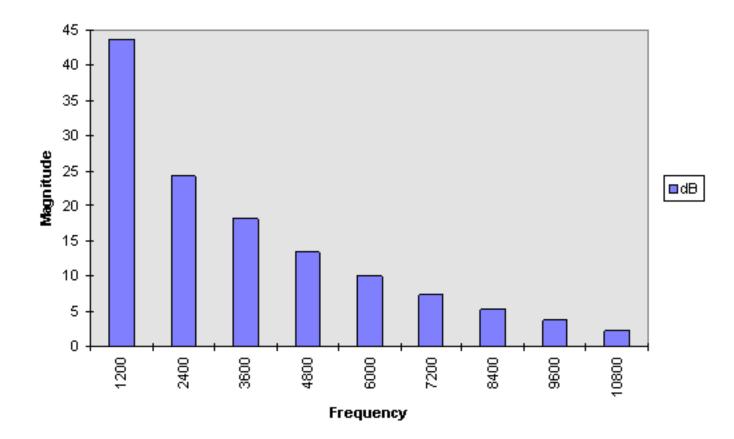

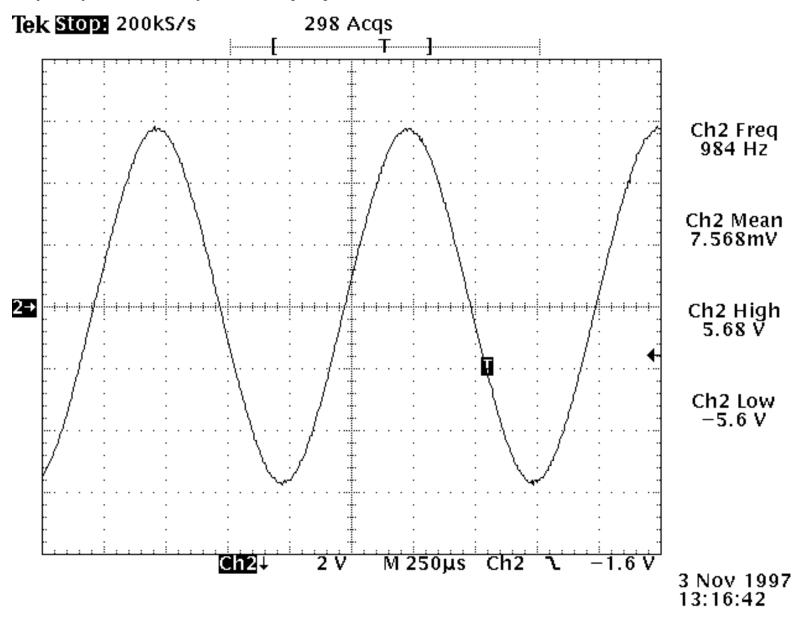

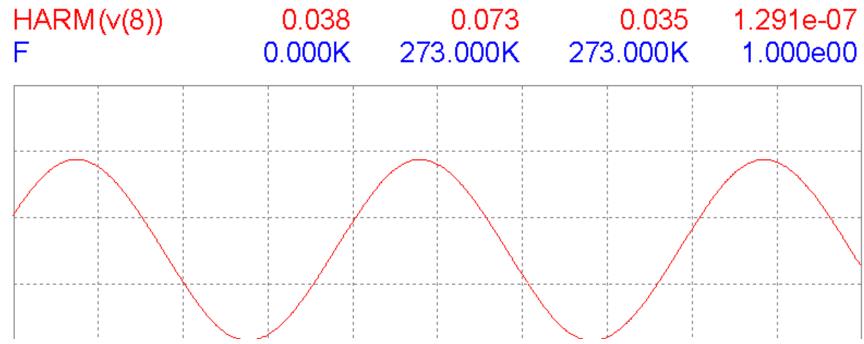

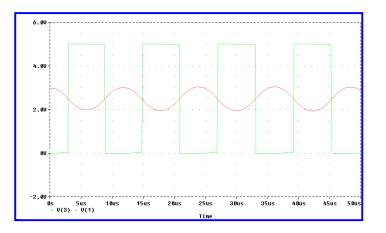

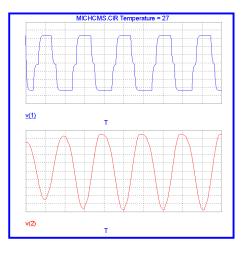

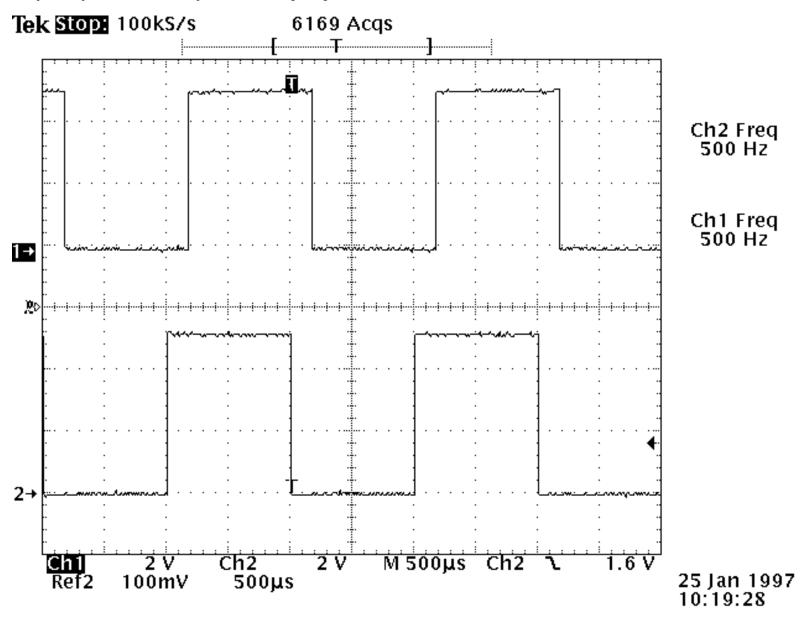

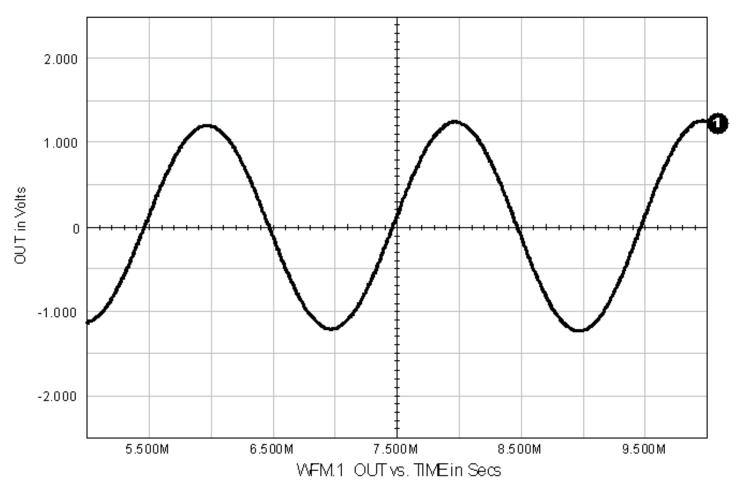

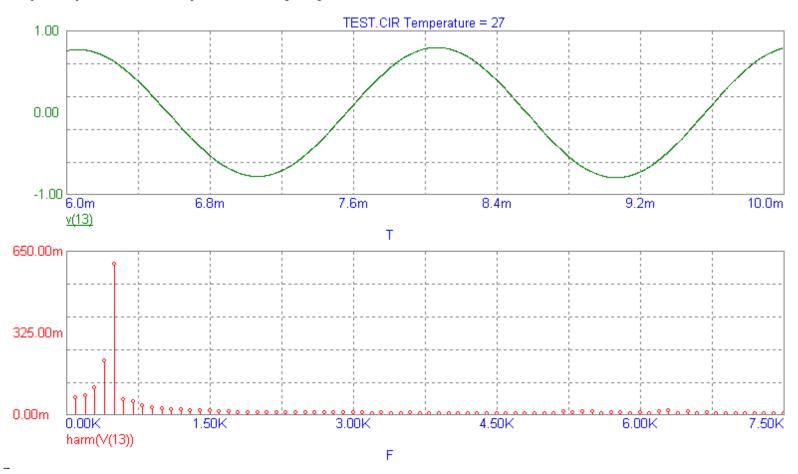

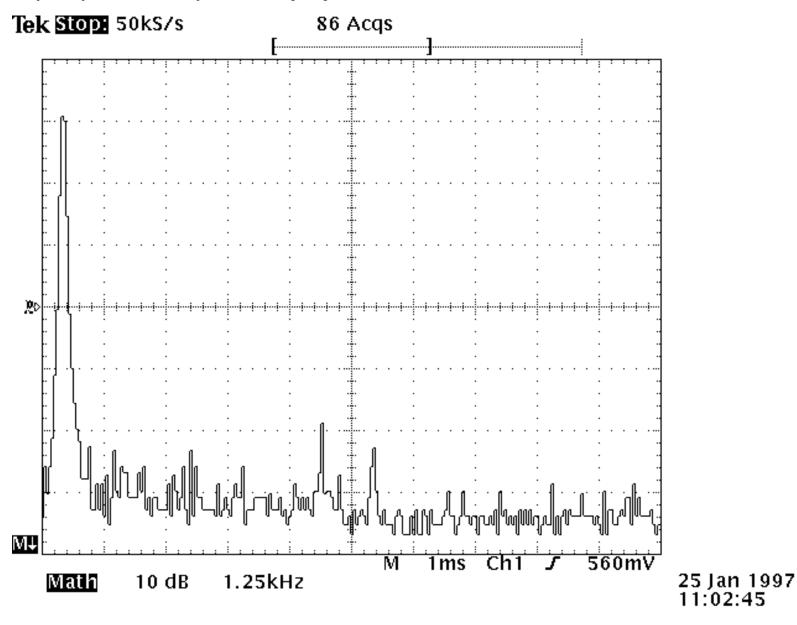

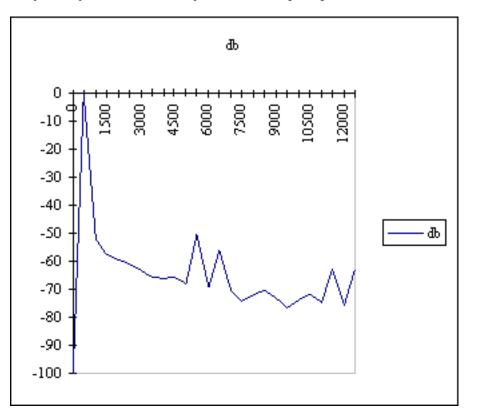

Figure 7-6: 2500Hz Square Wave Input, and Sine Wave Output

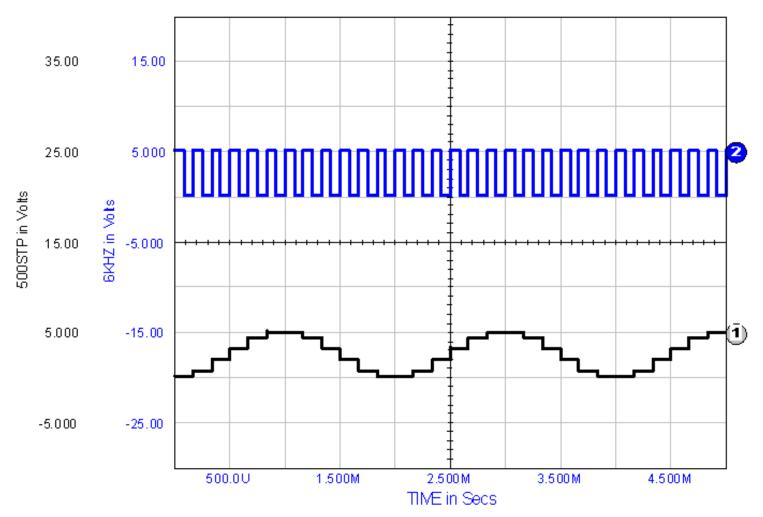

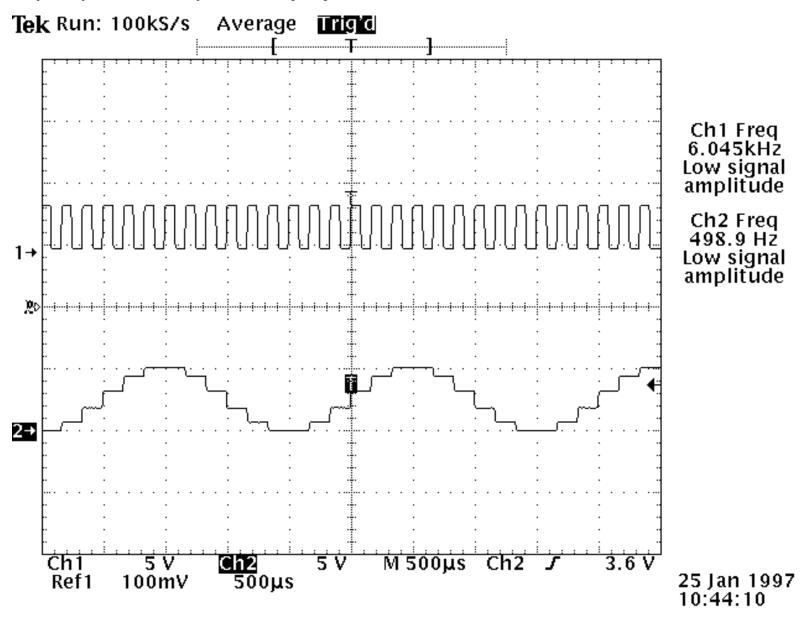

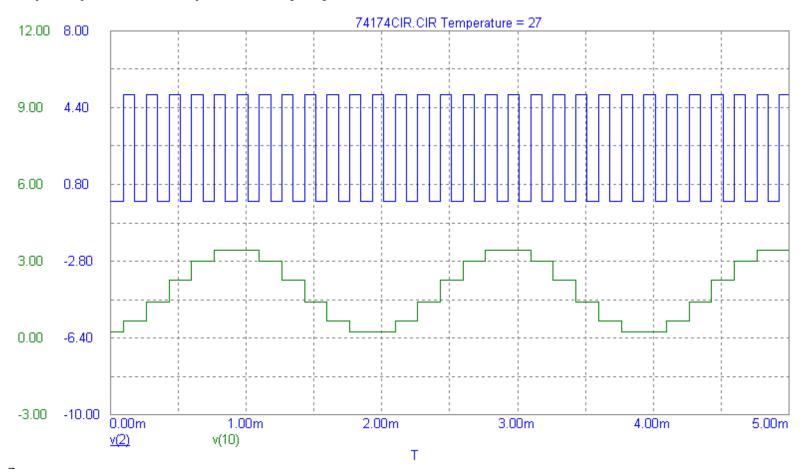

Figure 7-7: Ispice 2500Hz Square Wave Input, and Sine Wave Output

http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-08.php (7 of 9) [19/01/2002 22:02:07]

Figure 7-8: Micro-Cap 5 2500Hz Square Wave Input, and Sine Wave Output

Figure 7-9: Pspice 2500Hz Square Wave Input, and Sine Wave Output

| Condition              | Hardware | Micro-Cap V | Ispice  | Pspice   |

|------------------------|----------|-------------|---------|----------|

| Center Frequency       | 2.45 KHz | 2.42KHz     | 2.4 KHz | 2.44 KHz |

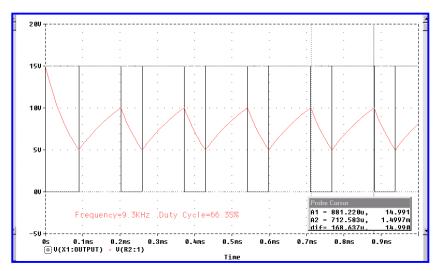

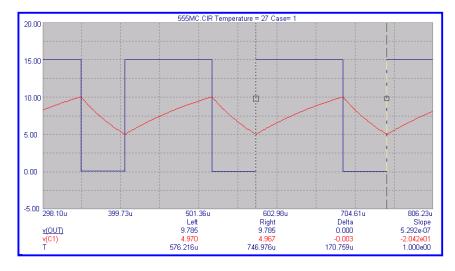

| Maximum<br>Attenuation | 0 dB     | 0.316 dB    | 0.44 dB | 0.886 dB |

| File Name              | NA       | BP          | Cheby1  | BP_n2    |

| ,                      | ,        | ,           |         | ,        |

http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-08.php (8 of 9) [19/01/2002 22:02:07]

| Run Time AC<br>Analysis | NA | 2.816 Sec | 0.65 Sec | 0.84 Sec |

|-------------------------|----|-----------|----------|----------|

|-------------------------|----|-----------|----------|----------|

For more accuracy increase the number of points per division.

Copyright 2002, PCBCafe. 1-888-44-WEB-44 http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image783.gif

#### http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image785.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image786.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image787.gif [19/01/2002 22:02:09]

#### http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image789.gif

## http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image790.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-09.php

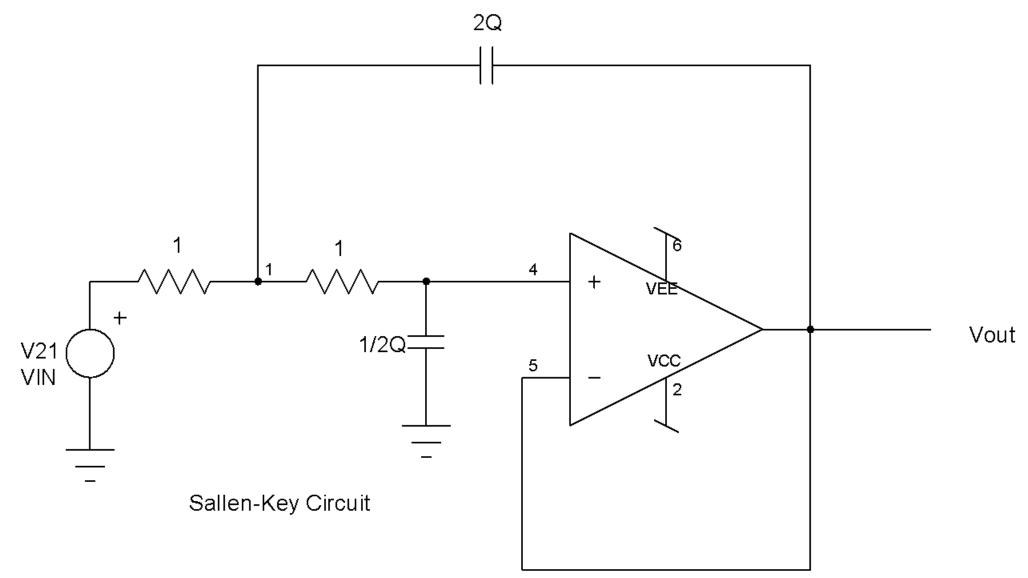

Figure 8-1: Sallen-Key Circuit

Figure 8-2: Chebyshev Lowpass Filter

#### $http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-09.php$

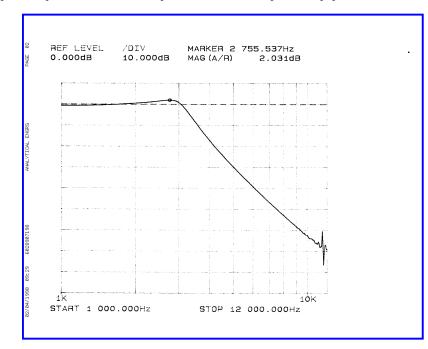

Figure 8-3: Chebyshev Lowpass Filter, Measured Data

Figure 8-4 Pspice Chebyshev Lowpass Filter Results

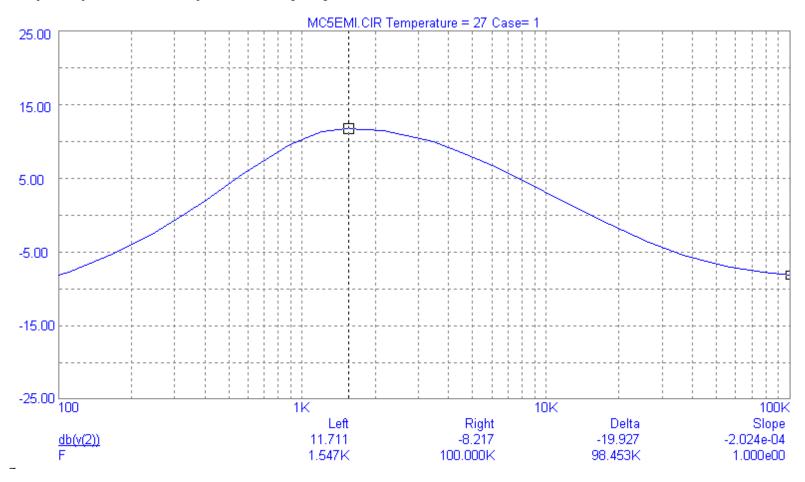

Figure 8-5: Ispice Chebyshev Lowpass Filter Results

$http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-09.php$

Figure 8-6: Micro-Cap V Chebyshev Lowpass Filter Results

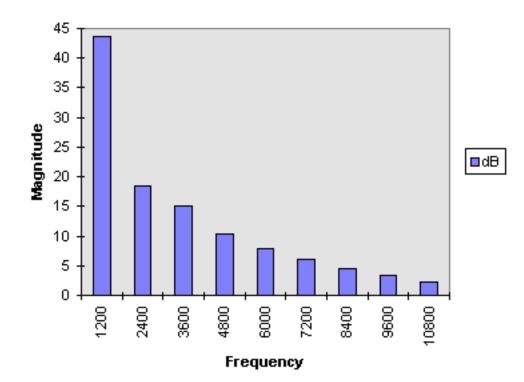

### **Table 8-1: Spice Statistics**

| Simulator   | File Name | Maximum Attenuation | Run<br>Time |

|-------------|-----------|---------------------|-------------|

| Hardware    | NA        | 2.03dB at 2.76KHz   | NA          |

| Pspice      | Lp_2      | 2.22dB at 2.75KHz   | 1.05sec     |

| Micro-Cap V | Lp        | 2.13dB at 2.67KHz   | 3.2sec      |

| Ispice      | Lp_n5     | 2.18dB at 2.70Khz   | 1.133sec    |

Copyright 2002, PCBCafe. 1-888-44-WEB-44

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image929.gif

$\omega_2 \coloneqq 29502 \cdot \pi$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image930.gif

$\omega_4 := 35002 \cdot \pi$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image931.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image932.gif

$\omega_1 \coloneqq 20502 \cdot n$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image933.gif

$\omega_3 \coloneqq 15002 \cdot \pi$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image934.gif

$\alpha_{min}$ :=22

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image935.gif

$$\omega_0^2 = \omega_1 \omega_2$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image936.gif

$$\omega_0 \coloneqq \sqrt{\omega_1 \cdot \omega_2}$$

$$\omega_{0 \text{freq}} = \frac{\omega_0}{2 \cdot \pi}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image940.gif

bw :=  $\omega_2 - \omega_1$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image942.gif

$$q_c = \frac{\omega_0}{bw}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image943.gif

$$q_c := \frac{\omega_0}{\omega_2 - \omega_1}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image945.gif

$$\Omega_s := \frac{\omega_4 - \omega_3}{\omega_2 - \omega_1}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image947.gif

$$\Omega_{\mathbf{p}} := -\left[\frac{-\left(\omega_{2}^{2}\right) + \omega_{0}^{2}}{\omega_{2} \cdot \left(\omega_{2} - \omega_{1}\right)}\right]$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image949.gif

$$\alpha_{\rm max} := 10 \frac{\left[ \left[ \cosh\left(n \cdot \operatorname{acosh}\left(\frac{\Omega_{\rm s}}{\Omega_{\rm p}}\right)\right)^2 + 10^{\left(\frac{1}{10} \cdot \alpha_{\rm min}\right)} - 1\right] \right]}{\ln(10)}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image950.gif

$$\alpha_{max} = 0.5$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image951.gif

$$\alpha_{\min} := 10 \frac{\ln \left[ \cosh \left( n \cdot \operatorname{acosh} \left\{ \frac{\Omega_s}{\Omega_p} \right\} \right)^2 \cdot 10^{\left\langle \frac{1}{10} \cdot \alpha_{\max} \right\rangle} + 1 - \cosh \left( n \cdot \operatorname{acosh} \left\{ \frac{\Omega_s}{\Omega_p} \right\} \right)^2 \right]}{\ln(10)}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image952.gif

$$\alpha_{\min} = 22$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image953.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image954.gif

n = 2.975

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image955.gif

ceil(n) = 3

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image956.gif

$n \coloneqq ceil(n)$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image957.gif

$$\psi := \begin{vmatrix} \frac{180}{2 \cdot n} & \text{if } \frac{n}{2} = \text{floor}\left(\frac{n}{2}\right) \\ \frac{180}{n} & \text{otherwise} \end{vmatrix}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image958.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image959.gif

$$\psi := \psi \cdot \frac{\pi}{180}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image960.gif

$\psi = 1.0$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image961.gif

$$\varepsilon := \left( \frac{\alpha_{\max}}{10} - 1 \right)^{\frac{1}{2}}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image963.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image964.gif

$$a := \frac{1}{n} \cdot \operatorname{asinh}\left(\frac{1}{\varepsilon}\right)$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image966.gif

$$\sigma_{s} \coloneqq |\sinh(a)|$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image968.gif

$$\sigma_{\mathbf{k}} \coloneqq | -\sinh(\mathbf{a}) \cdot \cos(\psi) |$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image970.gif

$$\omega_{\mathbf{k}} \coloneqq |\operatorname{cosh}(\mathbf{a}) \cdot \sin(\psi)|$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image972.gif

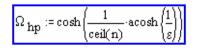

$$\Omega_{hp} := \cosh\left(\frac{1}{\operatorname{ceil}(n)} \cdot \operatorname{acosh}\left(\frac{1}{\varepsilon}\right)\right)$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image974.gif

$$\Sigma := |\sigma_k|$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image976.gif

$$\Omega \coloneqq |\omega_{\mathbf{k}}|$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image978.gif

$$C := \Sigma^2 + \Omega^2$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image980.gif

$$D := \frac{2 \cdot \Sigma}{q_c}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image982.gif

$$E := 4 + \frac{C}{q_c^2}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image984.gif

$$G := \sqrt{E^2 - 4 \cdot D^2}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image986.gif

$$Q := \frac{1}{D} \sqrt{\frac{1}{2}} (E + G)$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image988.gif

$$K := \frac{\sum Q}{q_c}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image990.gif

$$W := K + \sqrt{K^2 - 1}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image992.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image994.gif

$$Q_0 := \frac{q_c}{\sigma_s}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image996.gif

$$\omega_{01} := \frac{1}{W} \cdot \omega_0$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image998.gif

$$C := 10^{-7}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image999.gif

$$K_{m1} := \frac{1}{2 \cdot Q \cdot C \cdot \omega_{01}}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1001.gif

$$K_{m2} := \frac{1}{2 \cdot Q_0 \cdot C \cdot \omega_0}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1003.gif

$$K_{m3} := \frac{1}{2 \cdot Q \cdot C \cdot \omega_{02}}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1005.gif

$$\mathbb{R}_{1} \coloneqq (\mathbb{T}_{1}) \cdot \mathbb{K}_{m1}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1007.gif

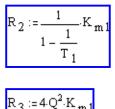

$$R_2 := \frac{1}{1 - \frac{1}{T_1}} K_{m1}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1009.gif

$$R_3 := 4 \cdot Q^2 \cdot K_{m1}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1011.gif

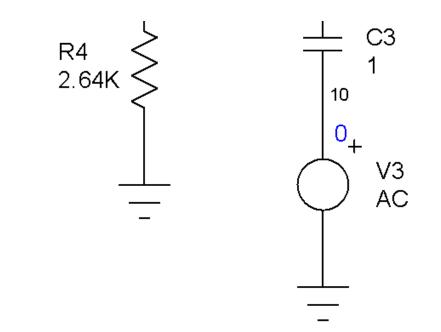

$$R_4 := T_2 K_m^2$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1013.gif

$$R_5 := \frac{1}{1 - \frac{1}{T_2}} K_{m2}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1015.gif

$$R_6 := 4 \cdot Q_0^2 \cdot K_{m2}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1017.gif

$$\mathbf{R}_7 \coloneqq (\mathbf{T}_3) \cdot \mathbf{K}_{m2}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1019.gif

$$R_8 := \frac{1}{1 - \frac{1}{T_3}} K_{m2}$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1021.gif

$$R_9 := 4 \cdot Q^2 \cdot K_m B$$

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1024.gif

## http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1026.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1027.gif (1 of 2) [19/01/2002 22:02:38]

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1027.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1029.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/Image1030.gif

http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-10.php

Free Evaluation

Expedition<sup>™</sup> Series

equest a free CD toda

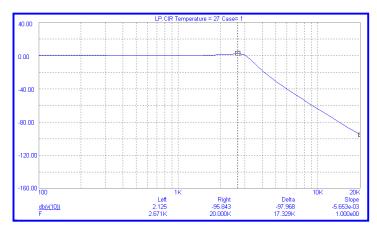

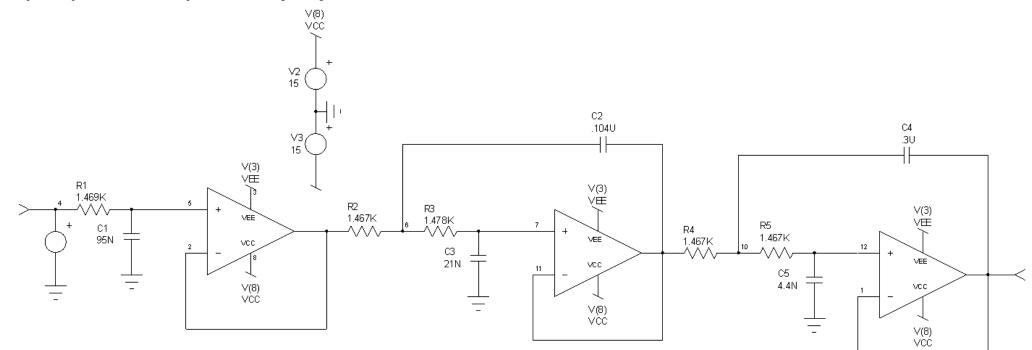

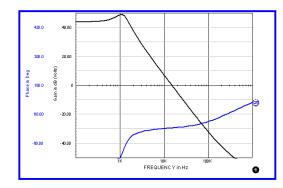

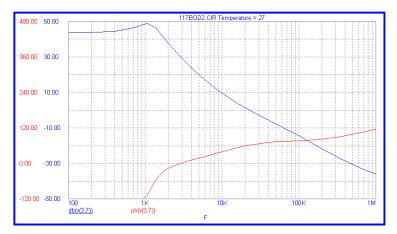

## **#9: Chebyshev Highpass Filter**

The Chebyshev filter response offers higher attenuation and a steeper rolloff near the cutoff frequency, than the Butterworth filter response. There is a tradeoff to achieve the higher attenuation. The cost of utilizing a Chebyshev filter is higher values of Q, which leads to difficulties in hardware realization, and nonlinear phase characteristics, which can result in difficulties in predicting circuit performance.

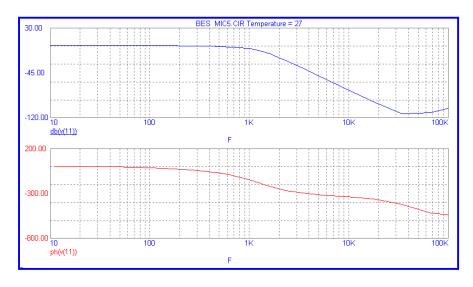

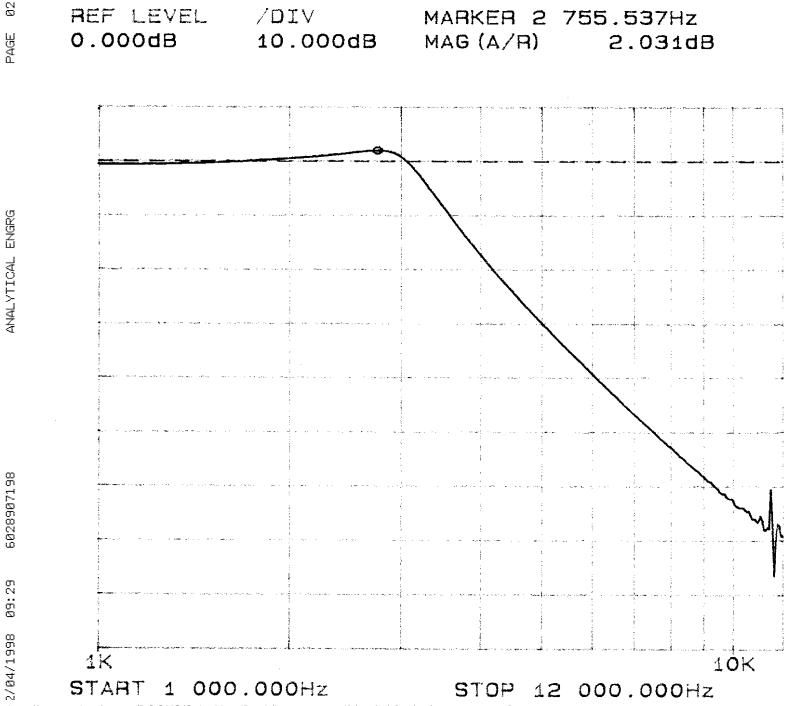

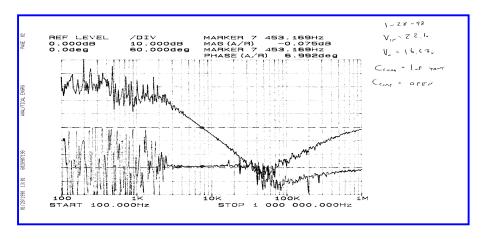

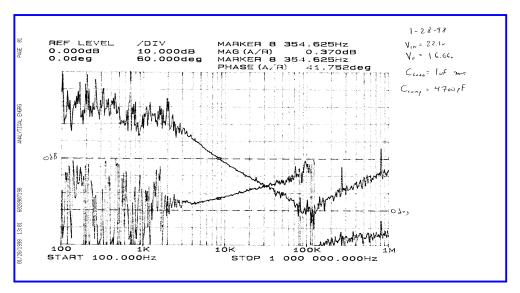

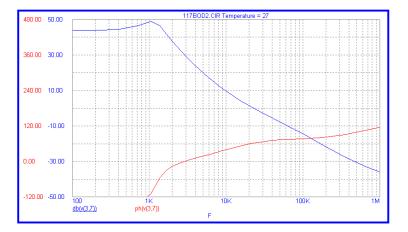

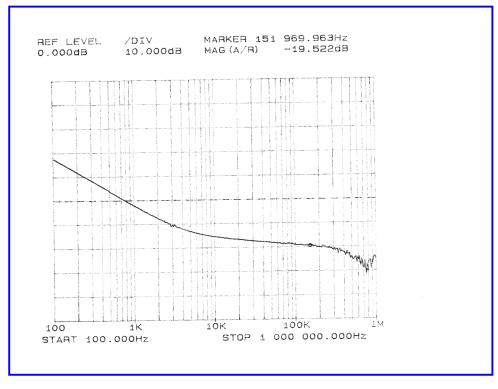

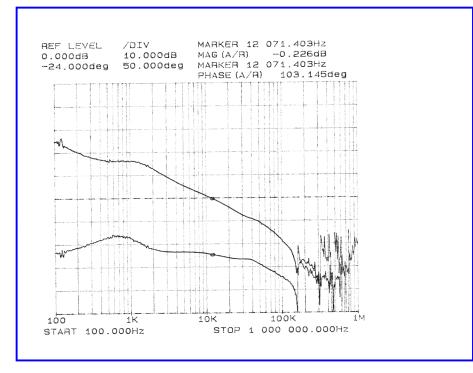

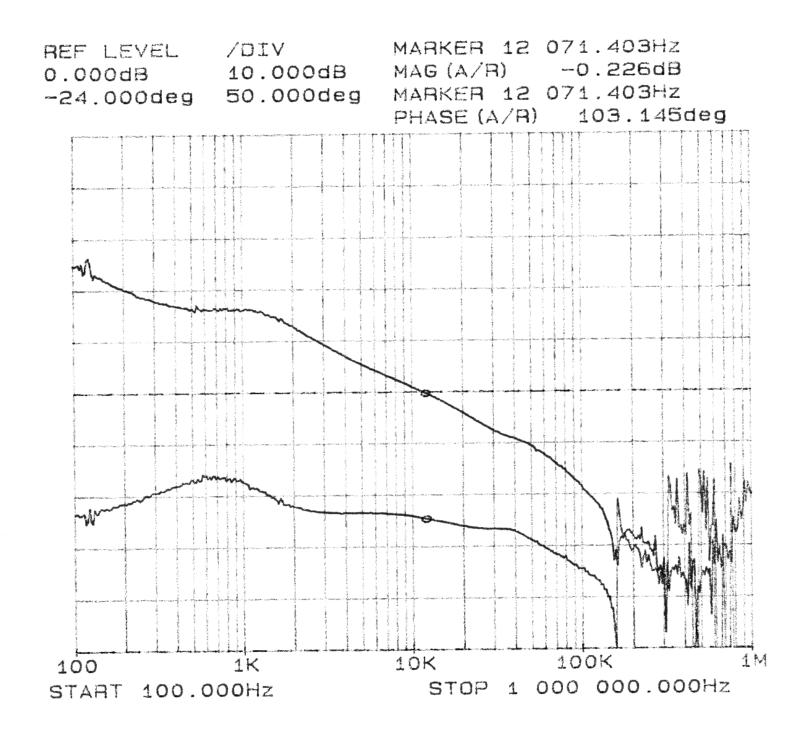

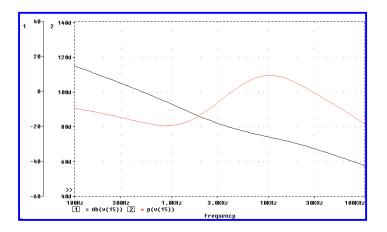

A Chebyshev highpass filter was constructed with the component values that are shown in the schematic in Figure 9-1. The measured results are shown in Figure 9-2, and Figure 9-3.

Figure 9-1: Chebyshev Highpass Filter

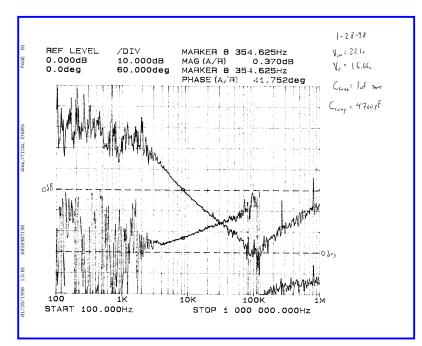

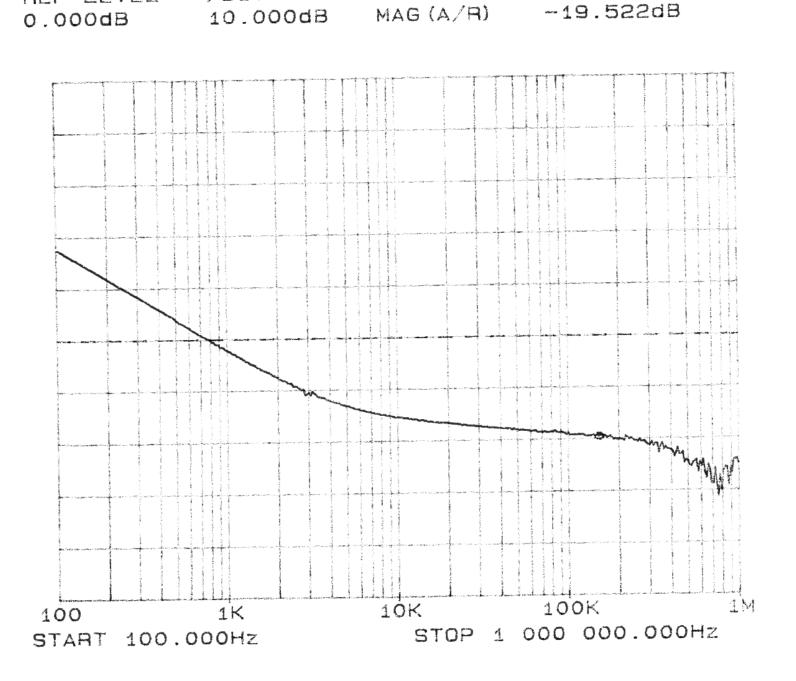

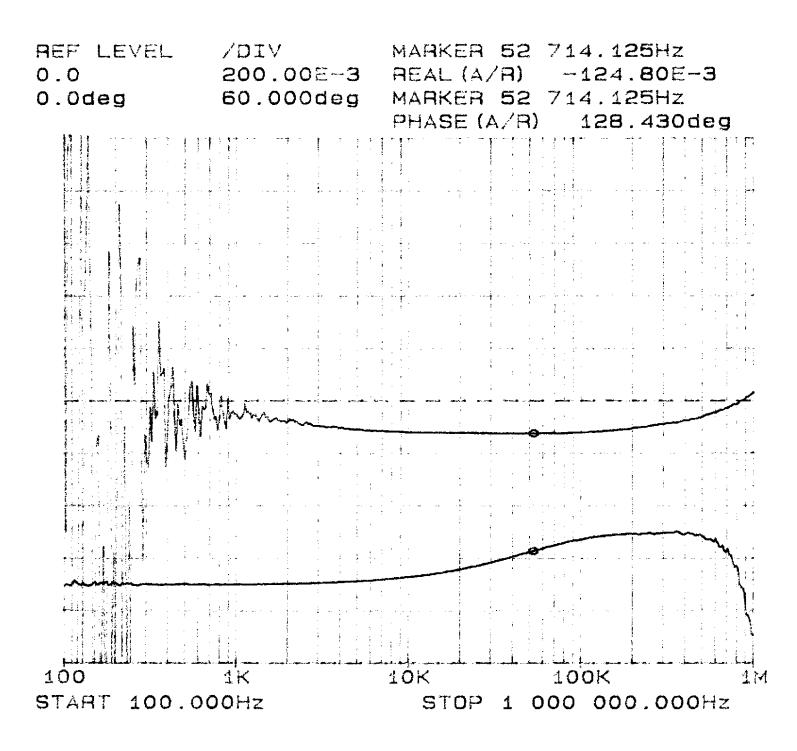

Figure 9-2: Chebyshev Highpass Filter Measured Results

Figure 9-3: Chebyshev Highpass Filter Measured Results

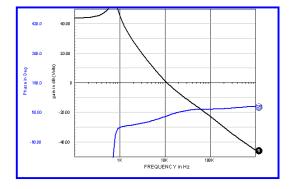

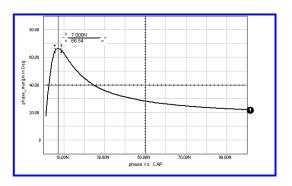

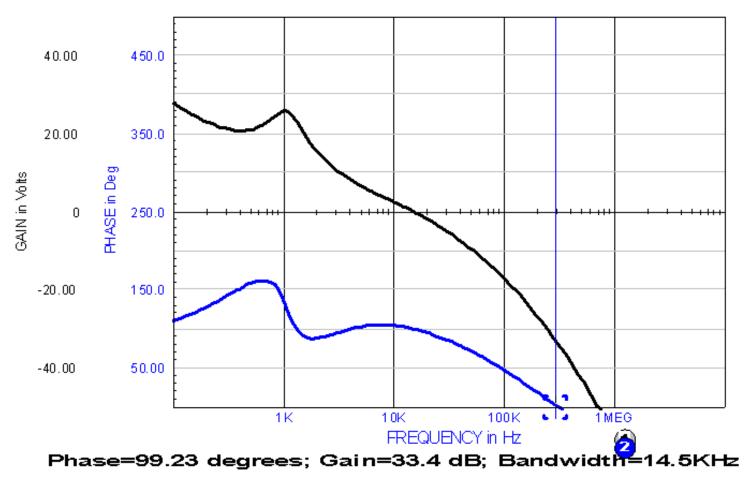

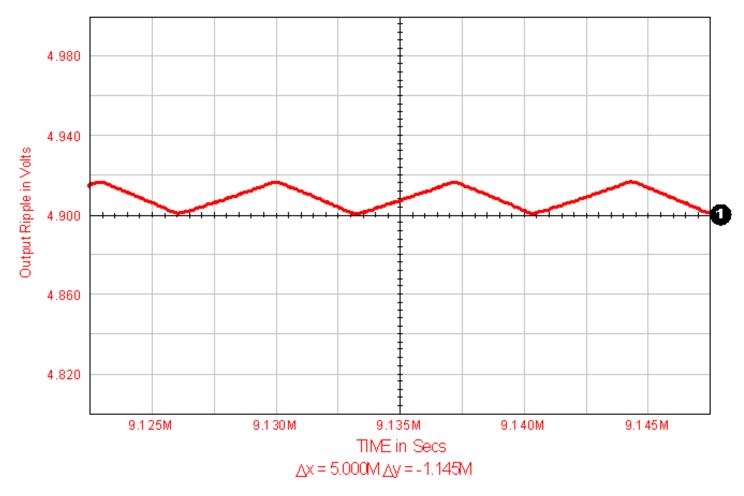

The results of the three simulators are shown in Figure 9-4 through Figure 9-7. All of the simulators accurately predict the phase and gain of the Chebyshev highpass circuit.

$http://www.pcbcafe.com/BOOKS/SpiceHandBook/04\_chapter03-10.php$

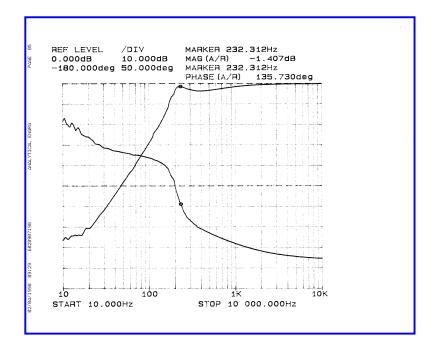

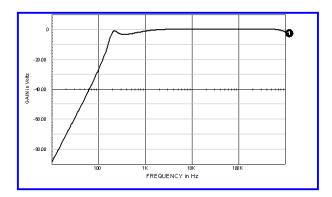

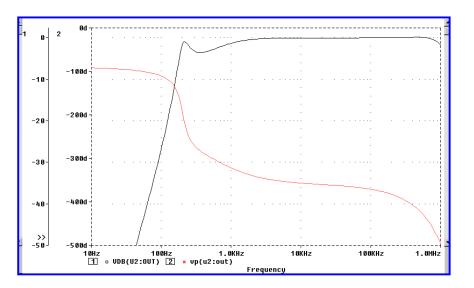

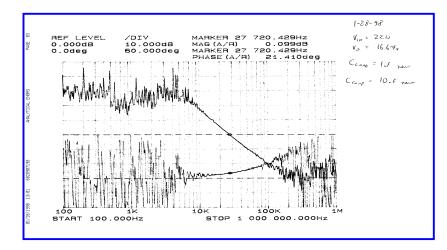

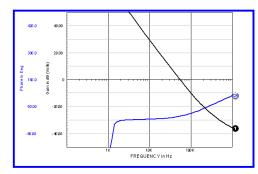

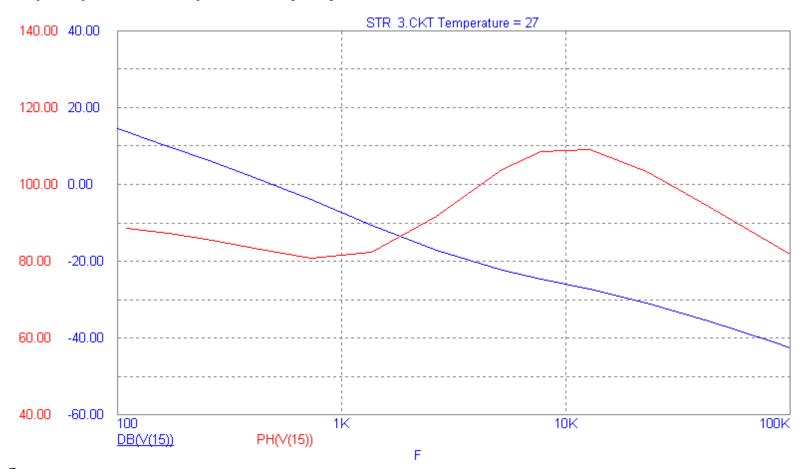

Figure 9-4: Ispice Chebyshev Highpass Filter

Figure 9-5: Ispice Chebyshev Highpass Filter

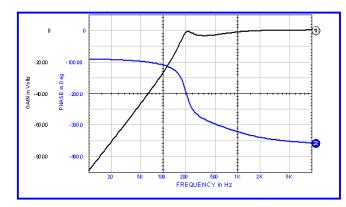

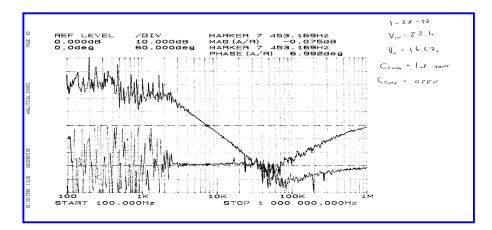

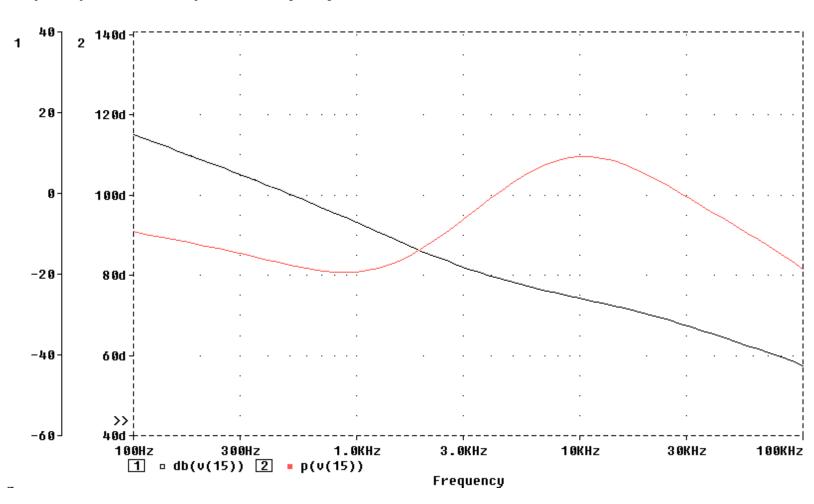

Figure 9-6: Pspice Chebyshev Highpass Filter

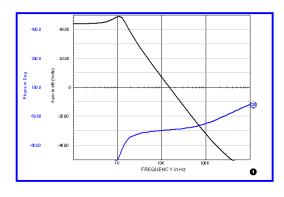

Figure 9-7: Micro-Cap V Chebyshev Highpass Filter

## **Table 9-1: Spice Statistics**

| Simulator   | File Name | Run Time  |

|-------------|-----------|-----------|

| Pspice      | hp_2      | 2.93 Sec  |

| Micro-Cap V | hp        | 1.728 Sec |

| Ispice      | hp_n2     | 1.166 Sec |

## References

Parker, Sybil, ed. 1984. Concise Encyclopedia of Science and Technology. New York: McGraw Hill

Van Valkenburg, M.E. 1982. Analog Filter Design. New York: Harcort Brace Jovanovich College Publishers.

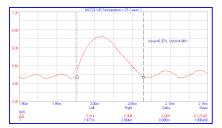

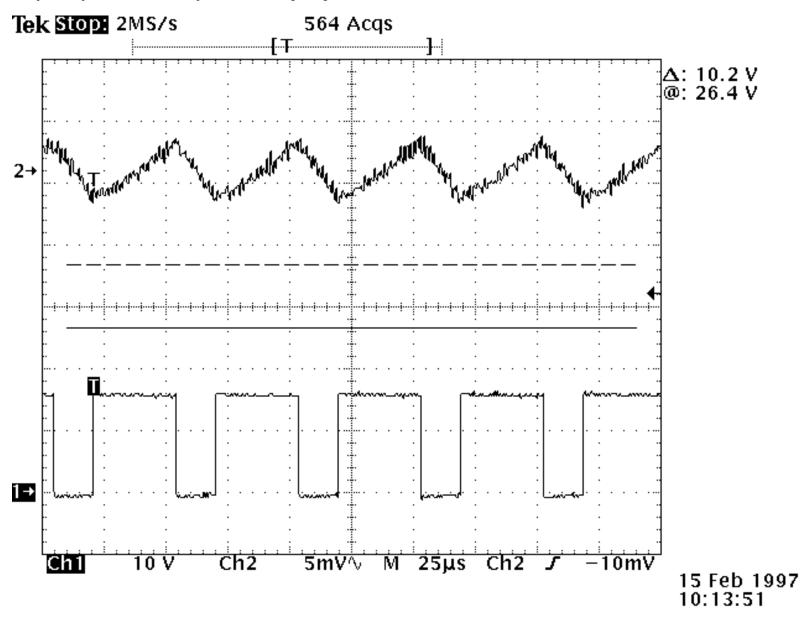

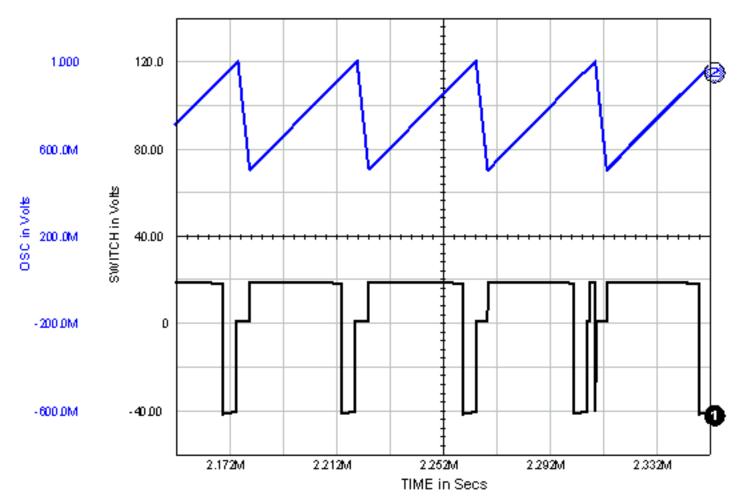

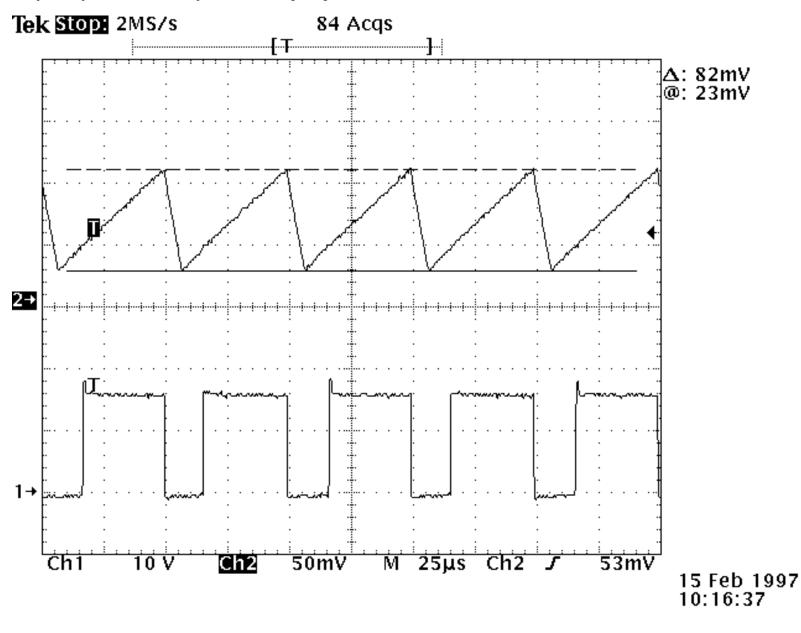

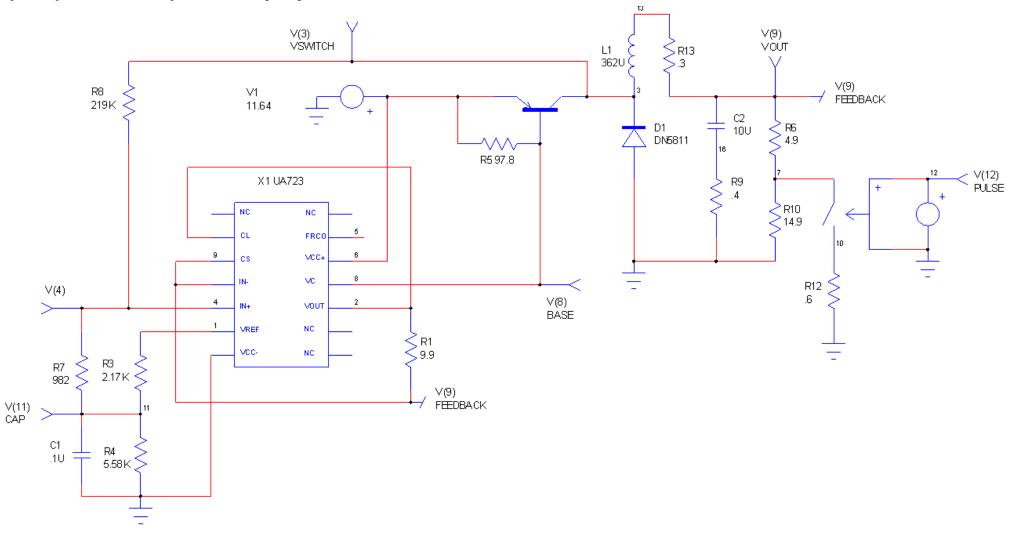

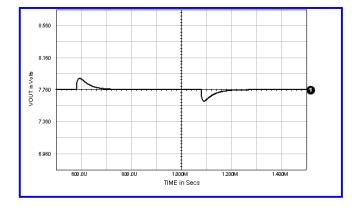

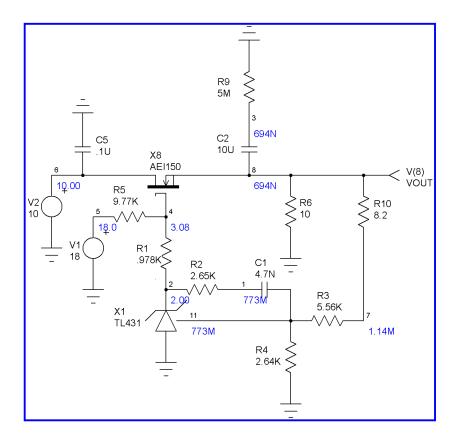

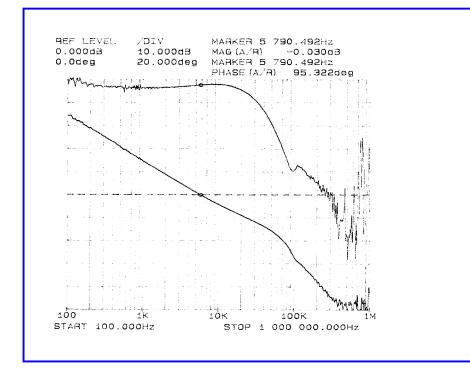

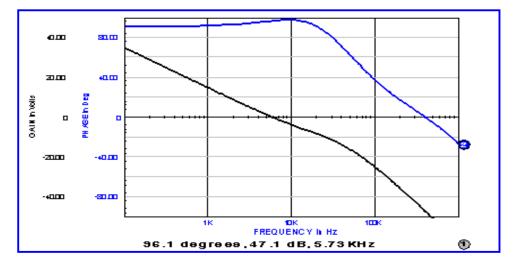

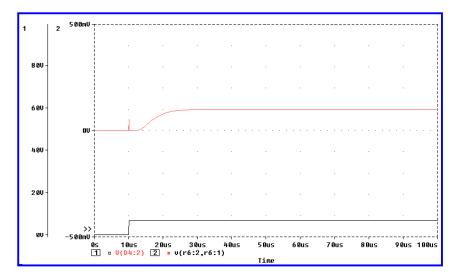

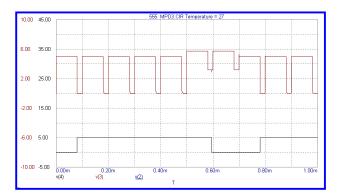

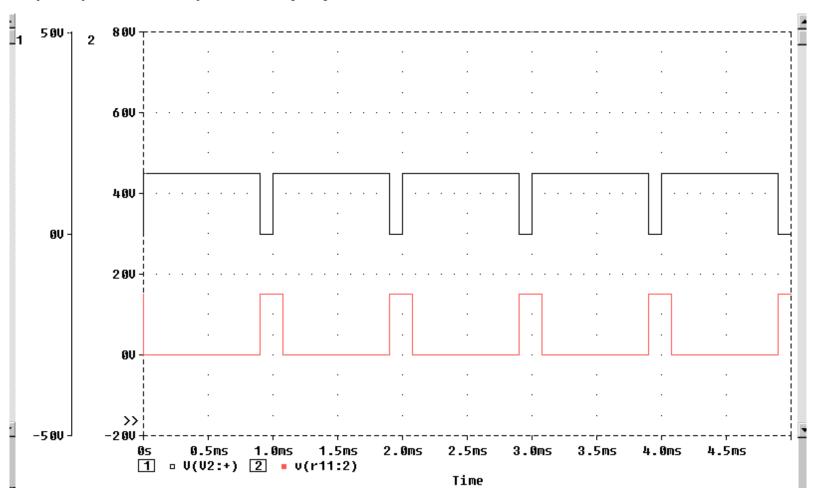

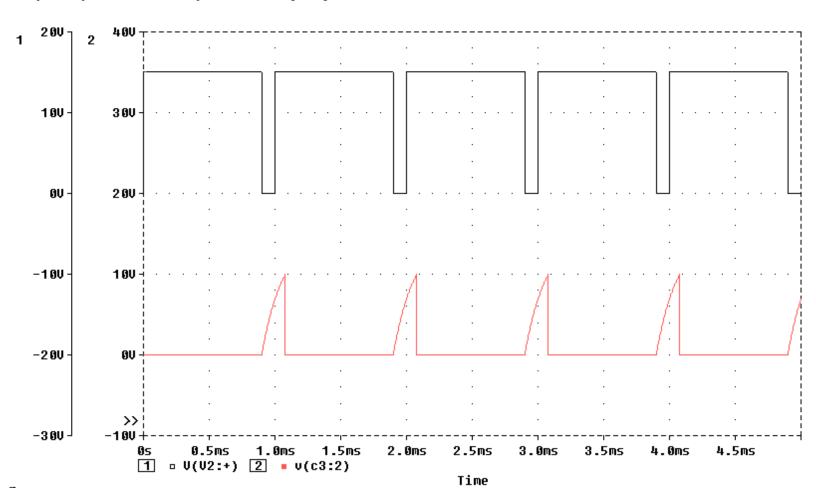

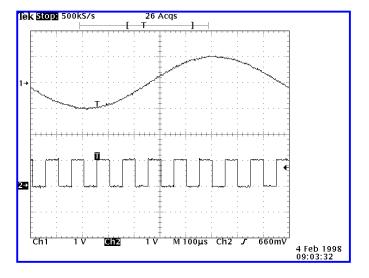

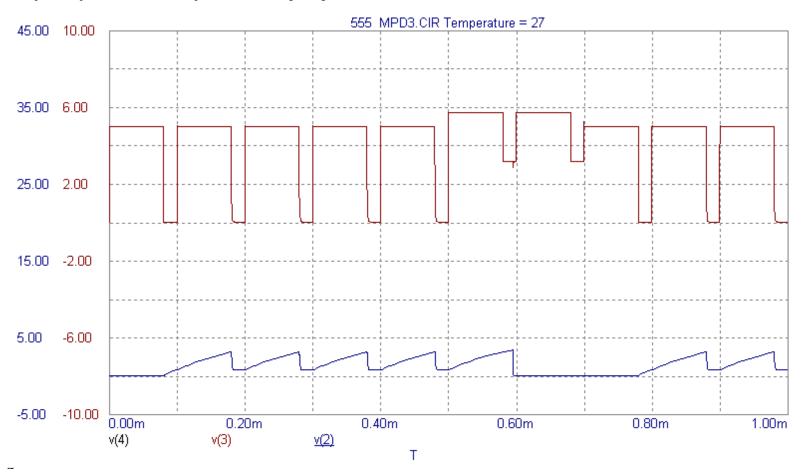

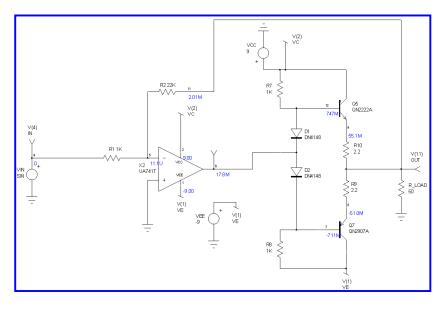

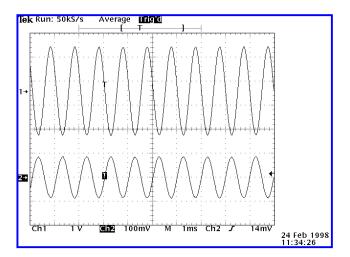

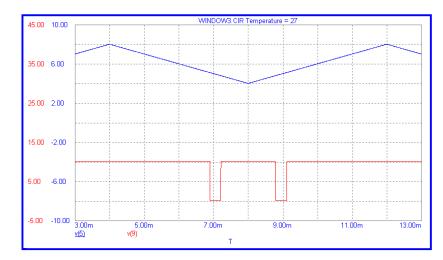

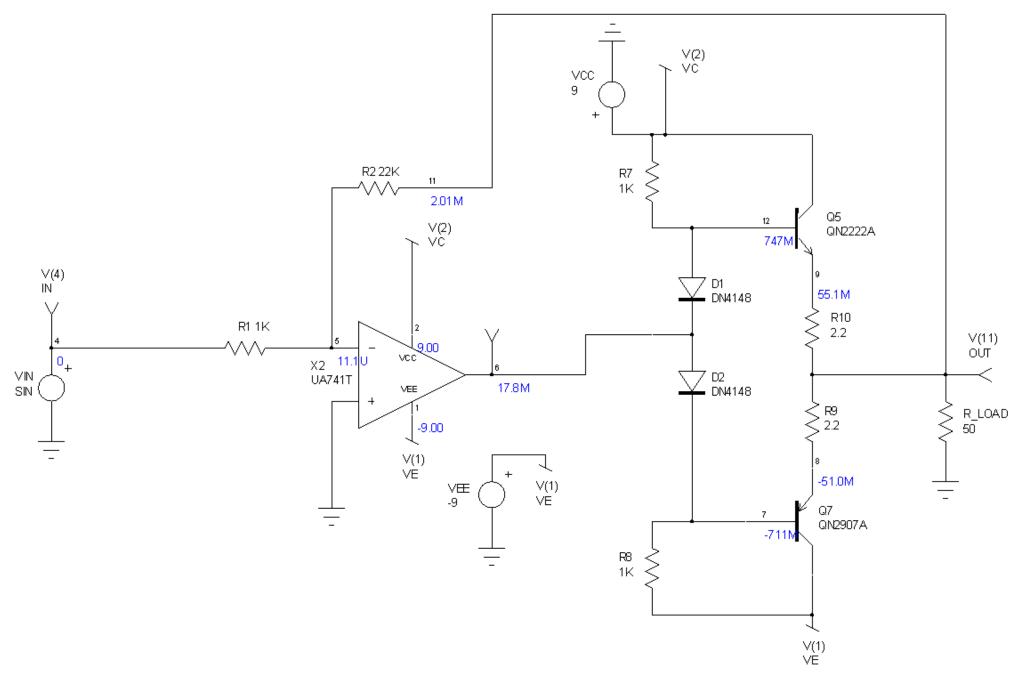

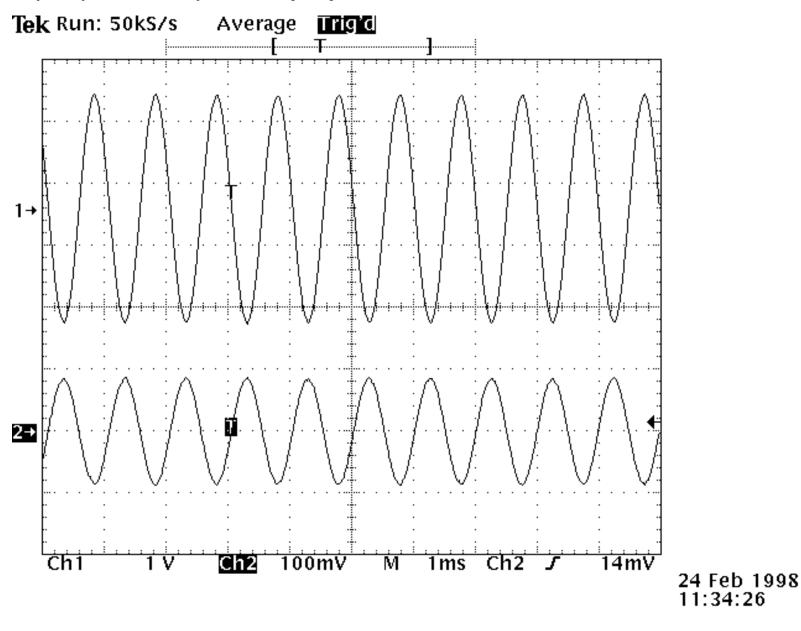

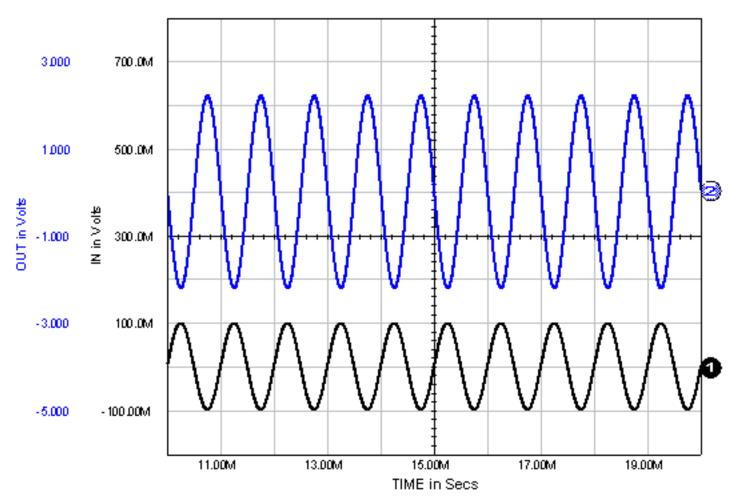

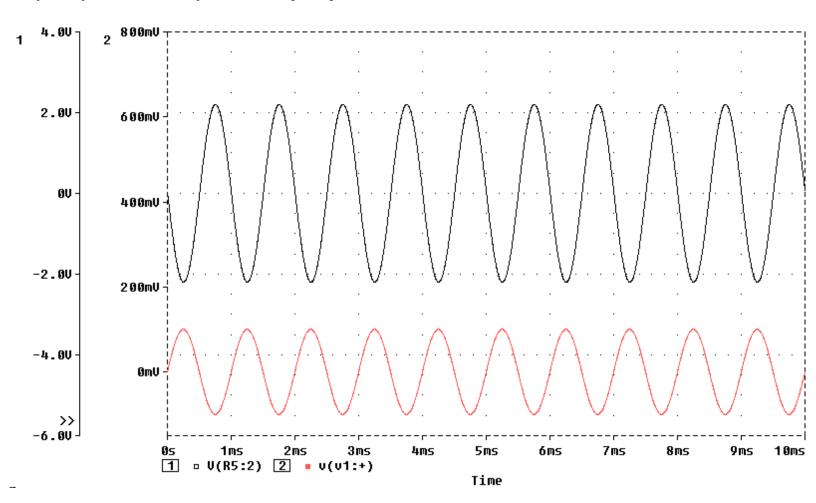

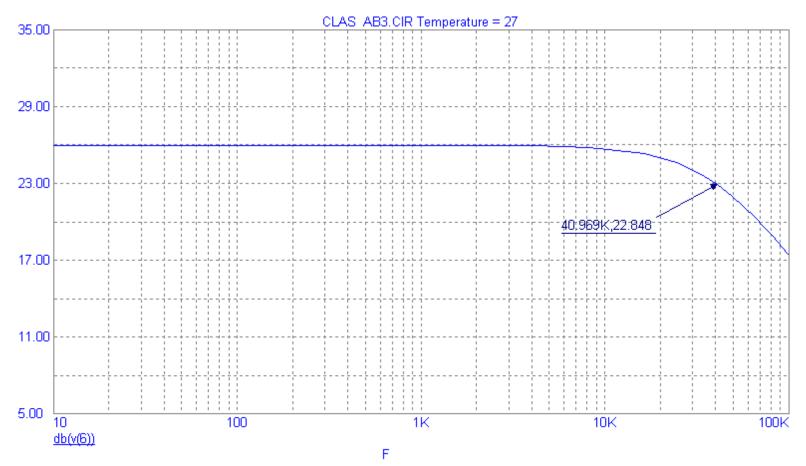

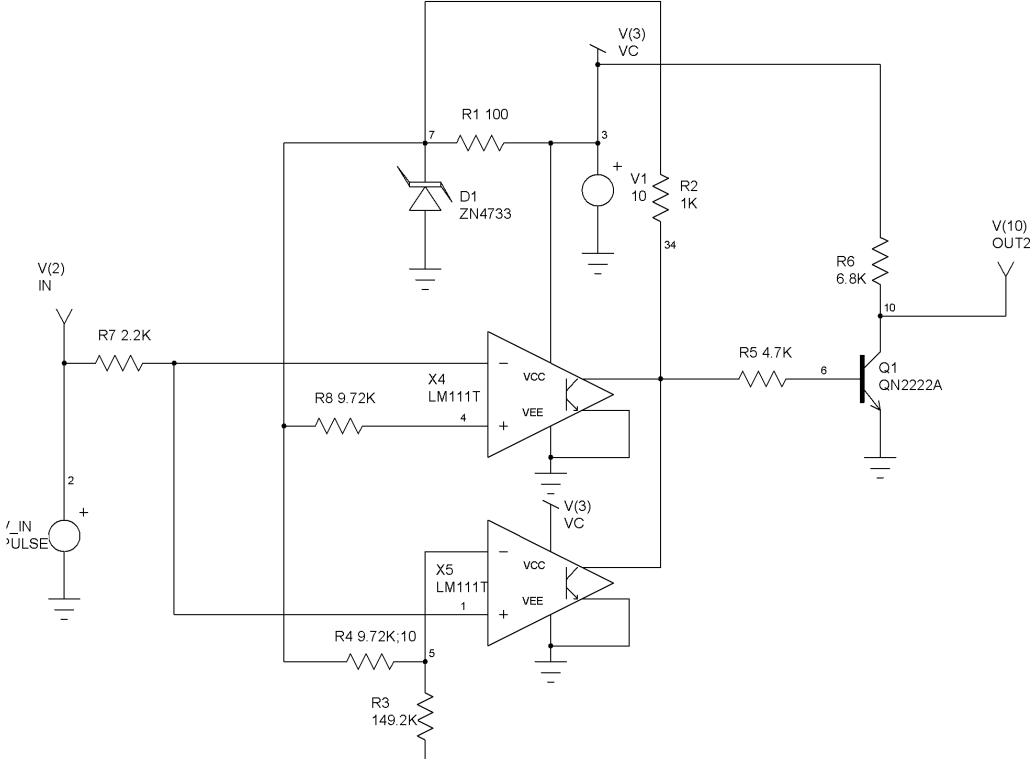

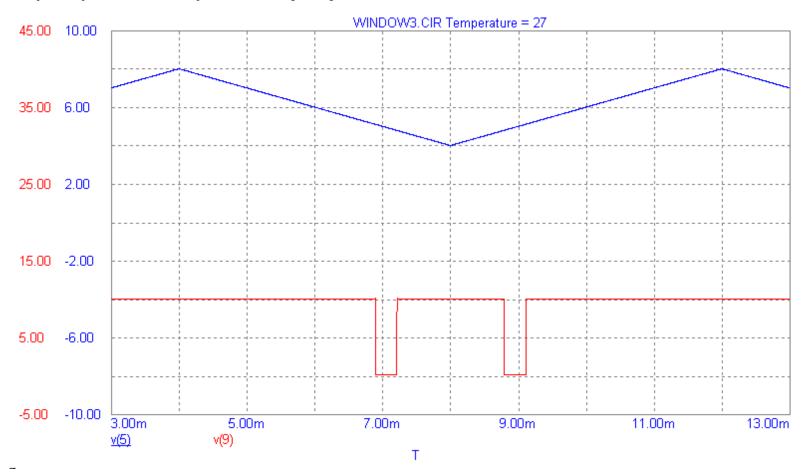

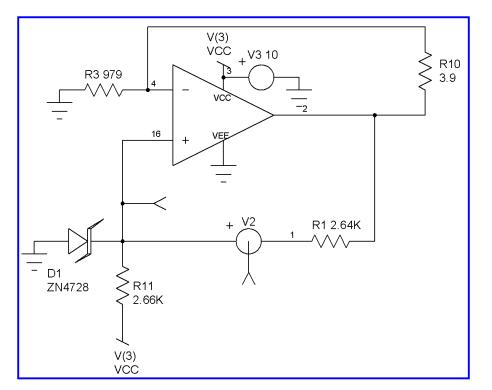

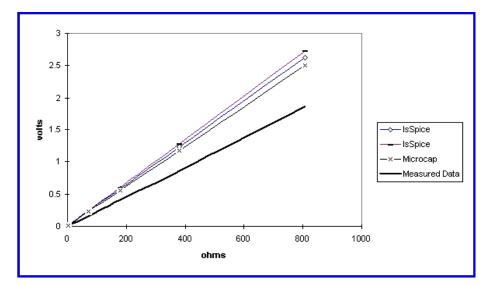

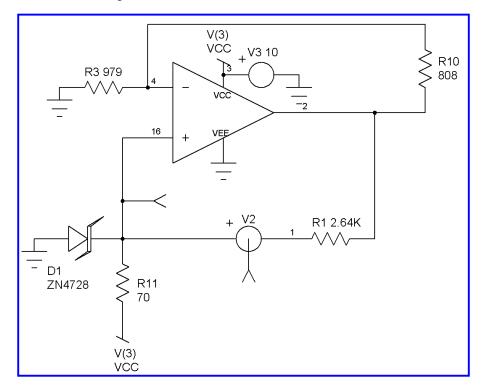

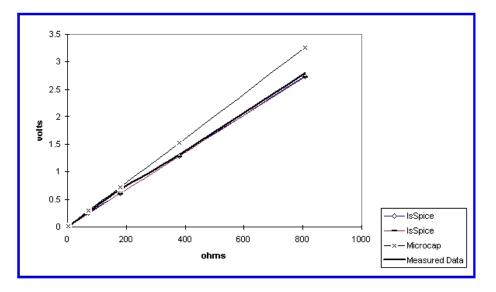

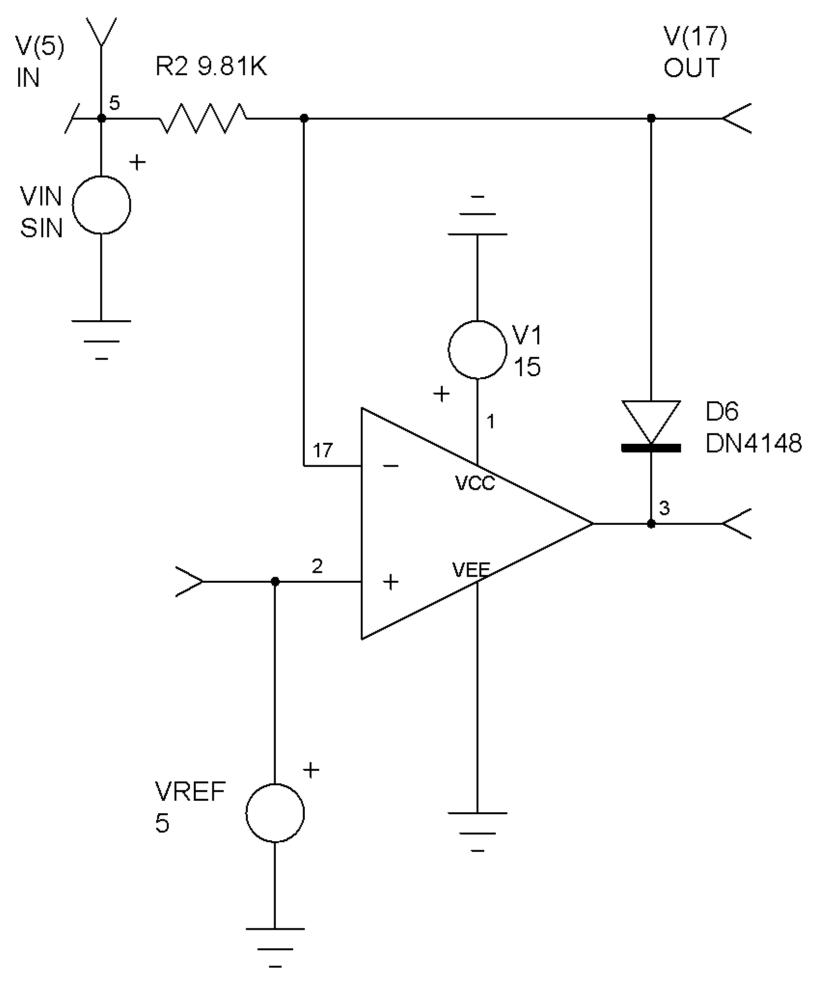

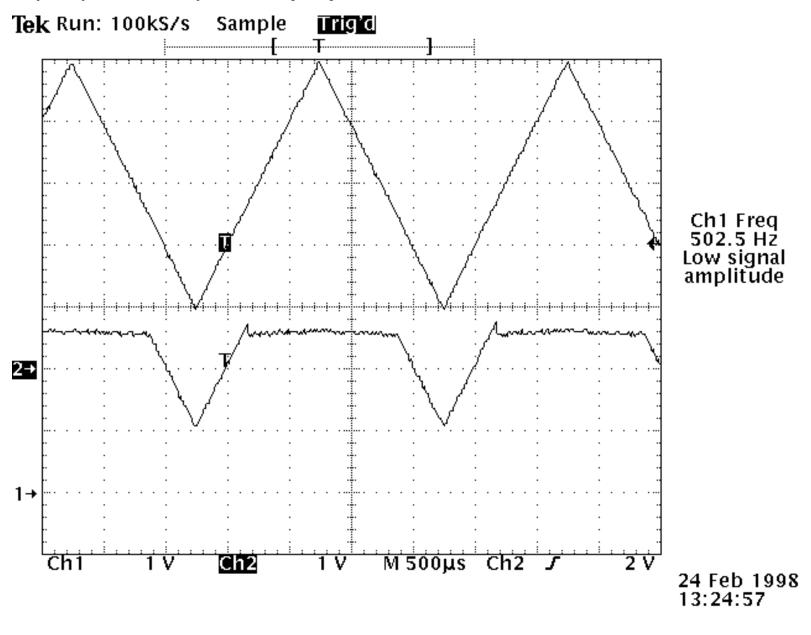

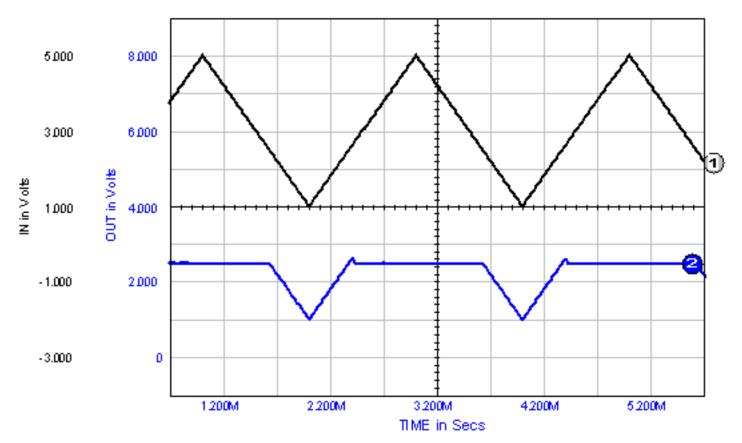

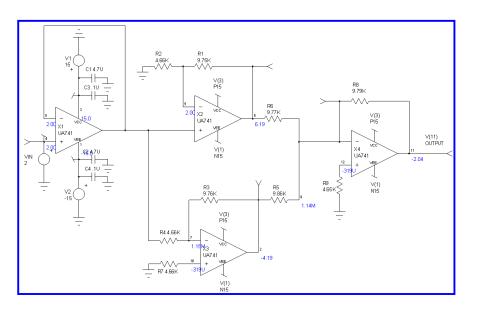

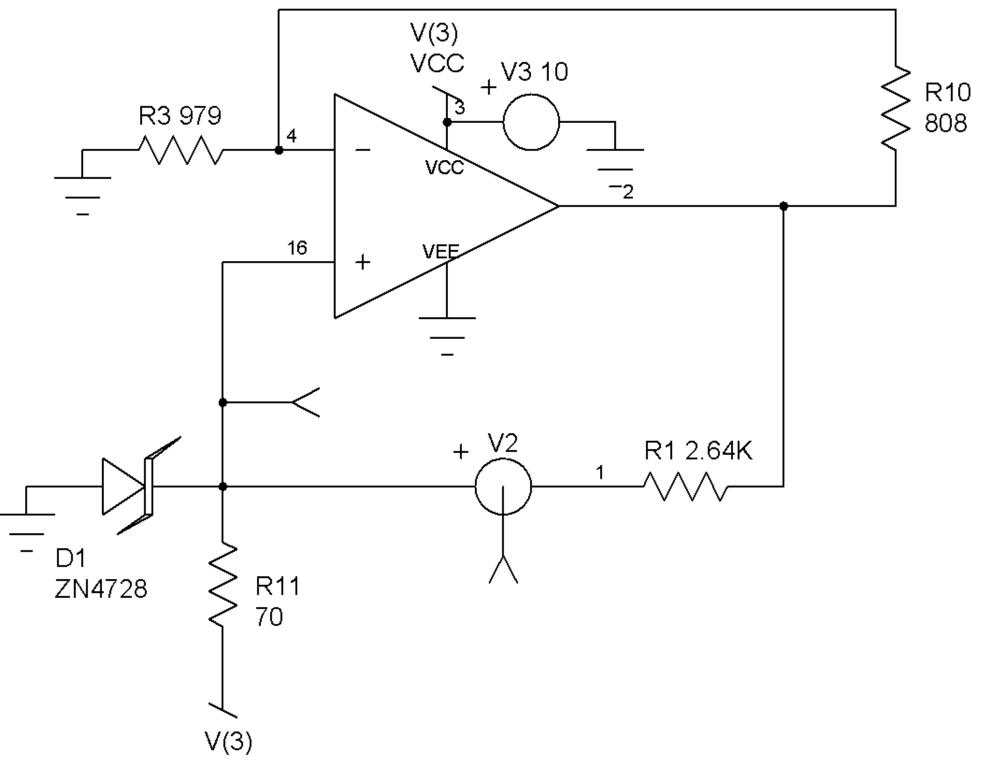

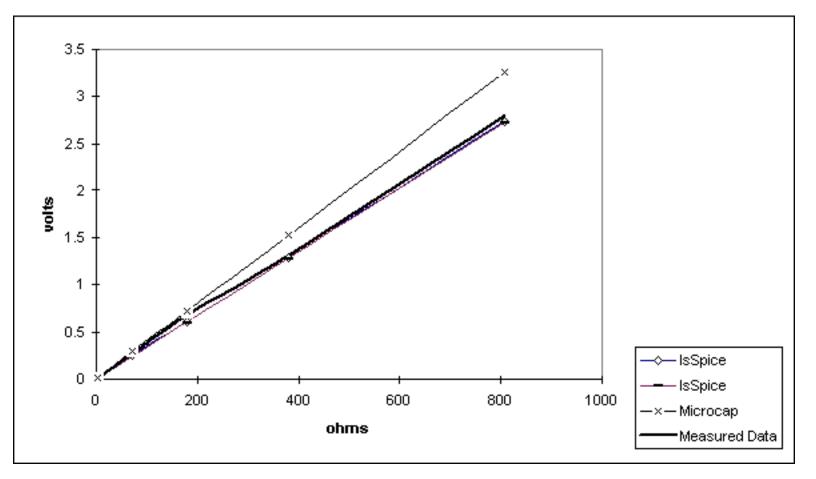

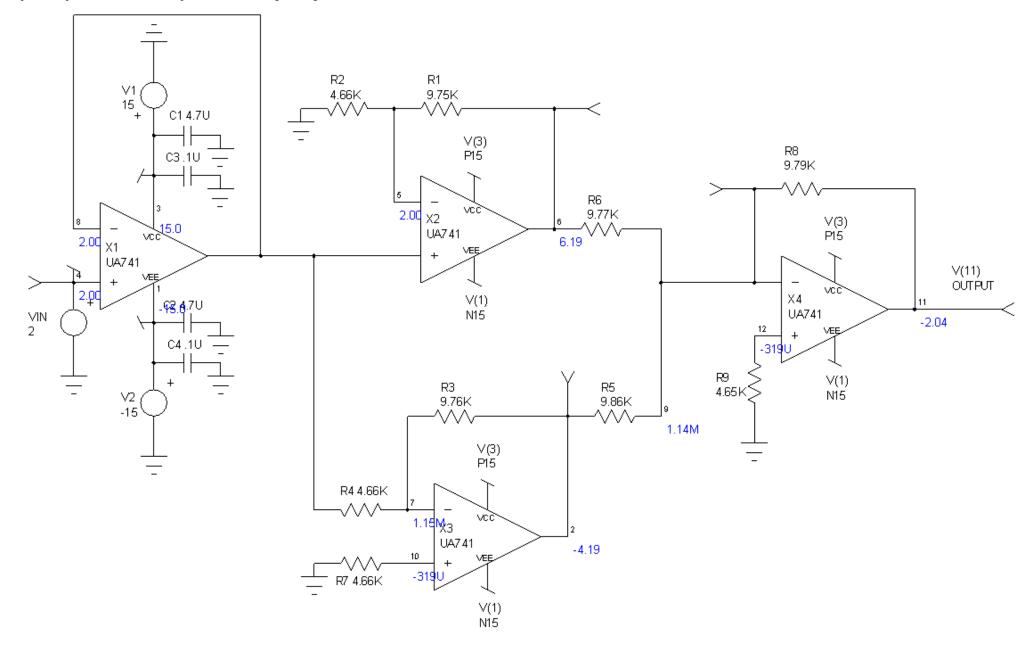

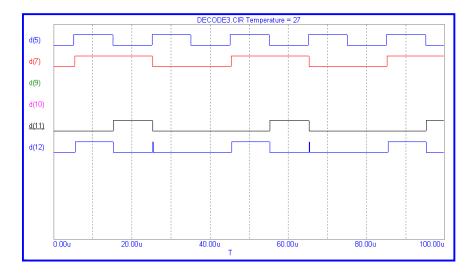

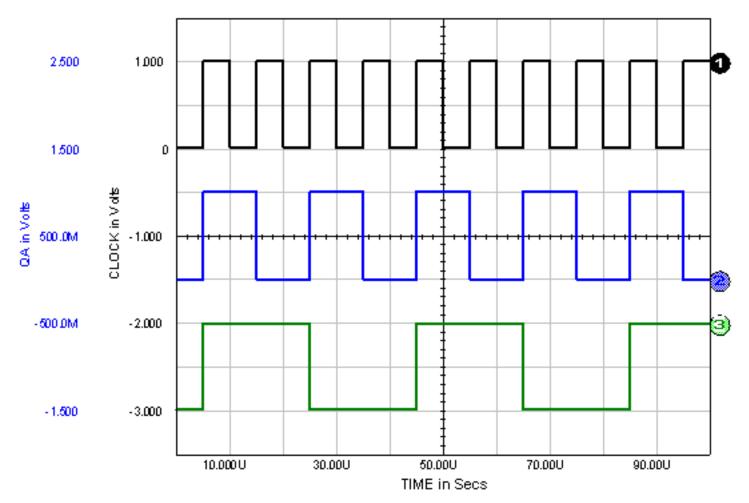

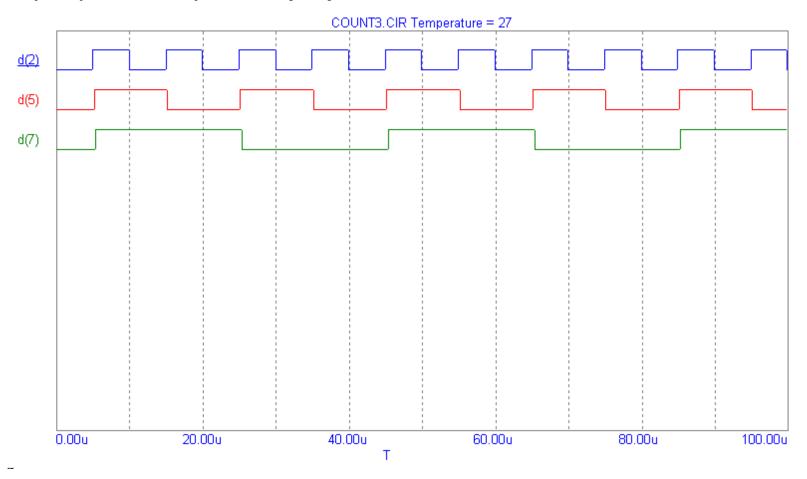

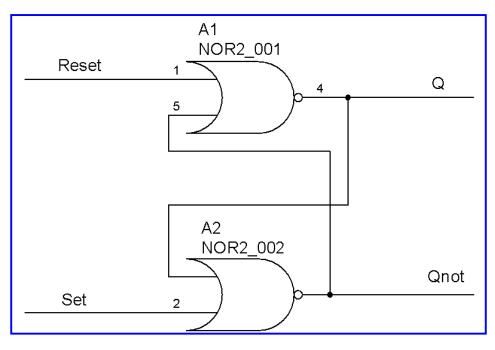

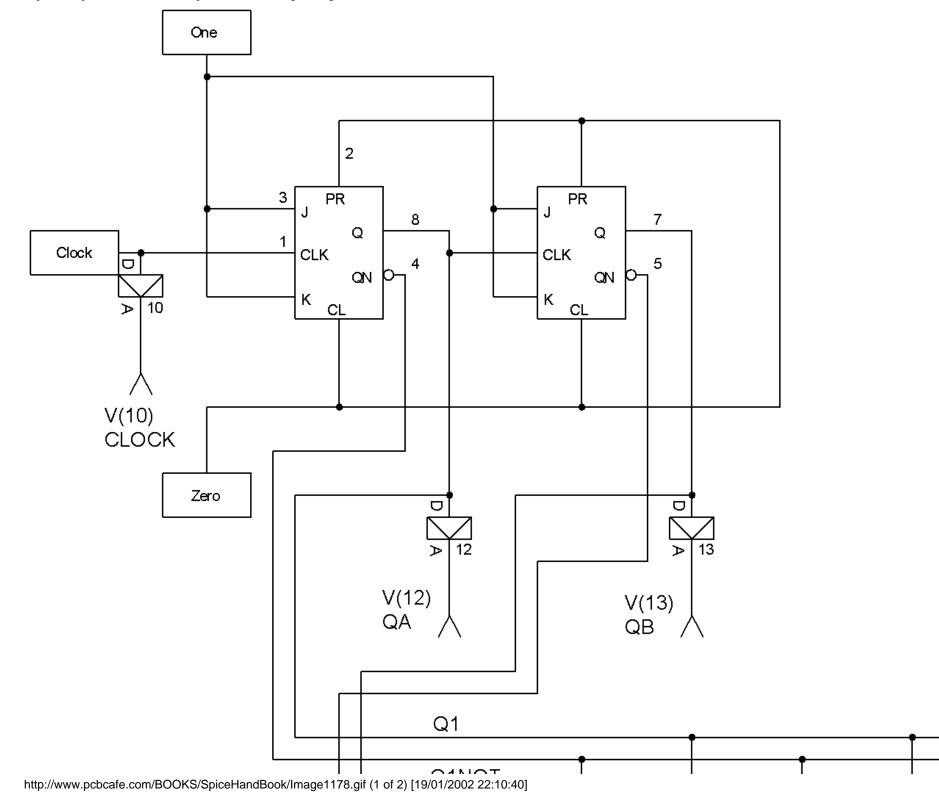

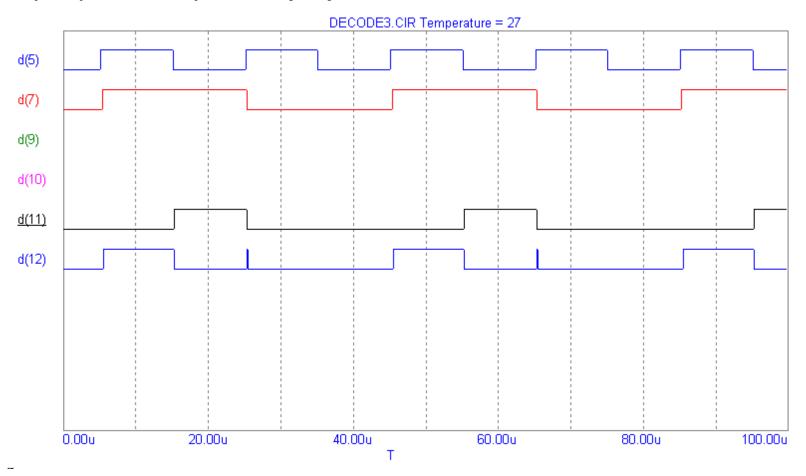

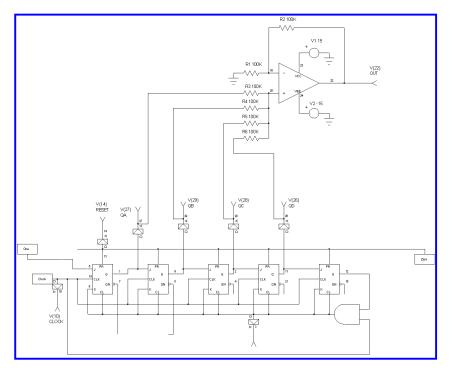

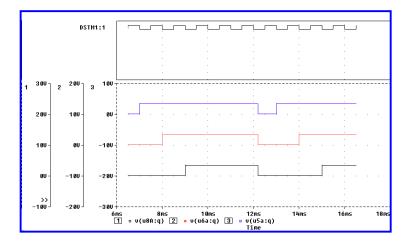

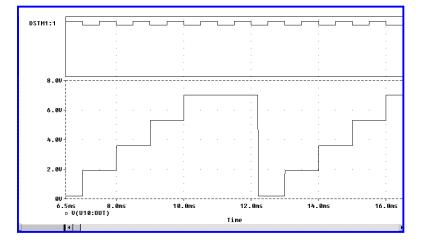

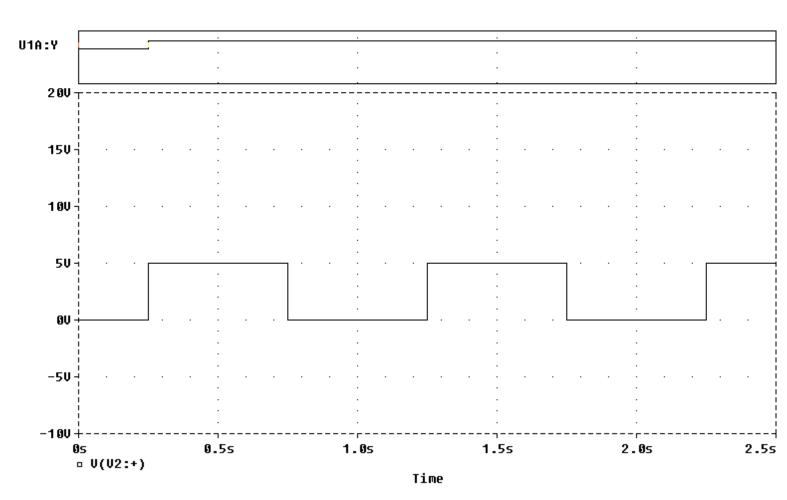

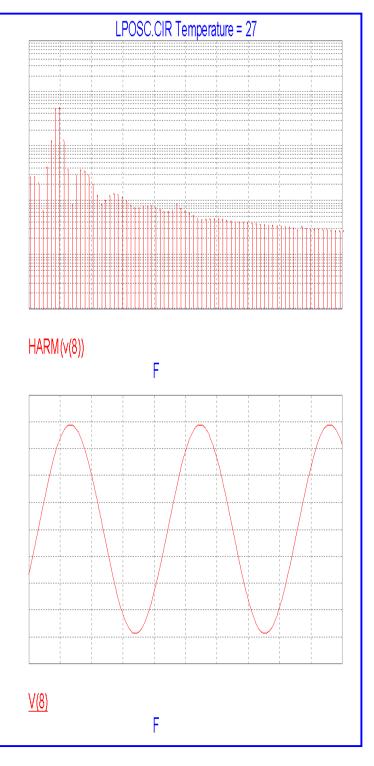

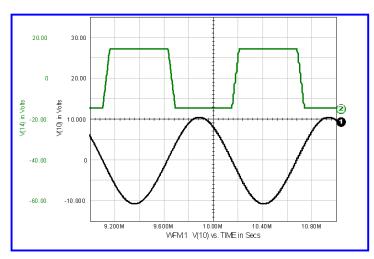

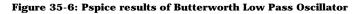

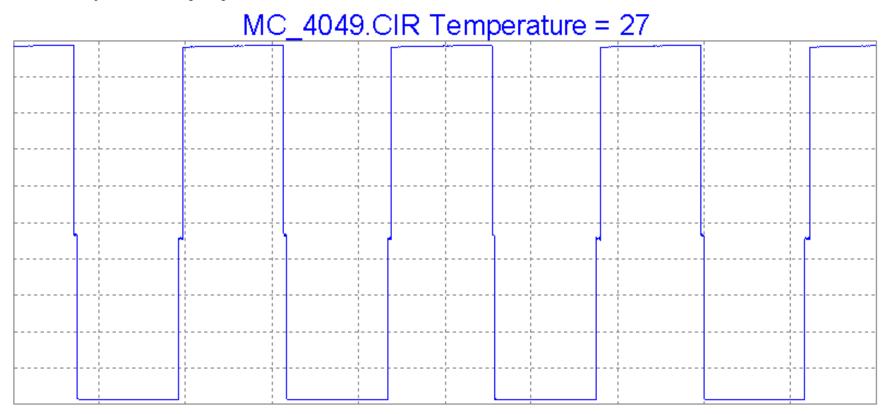

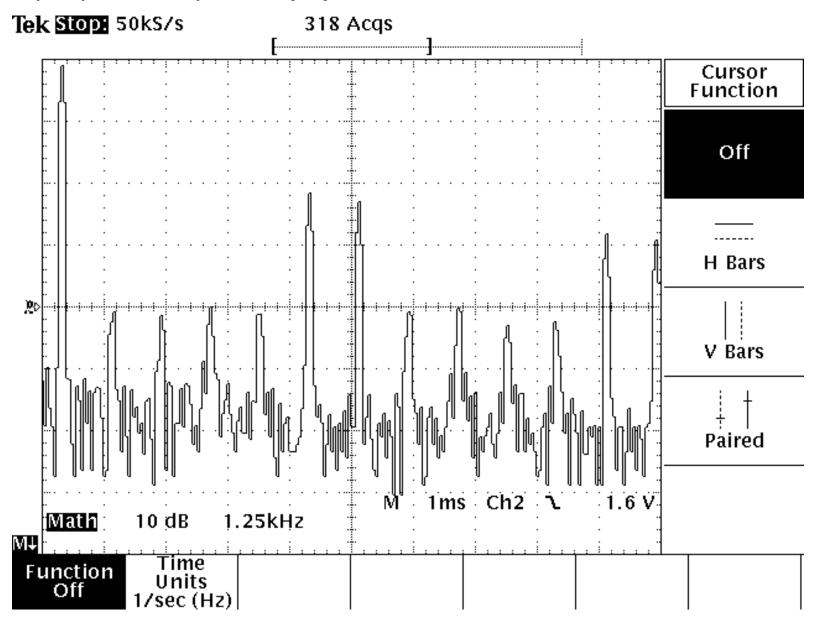

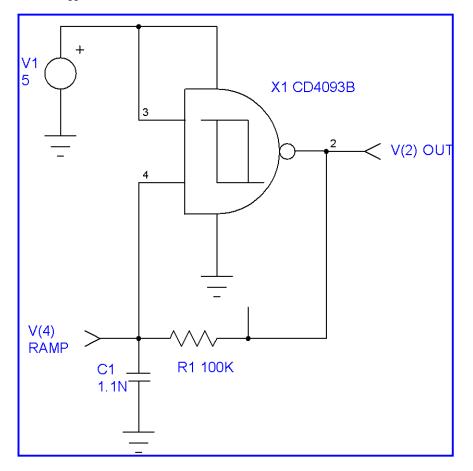

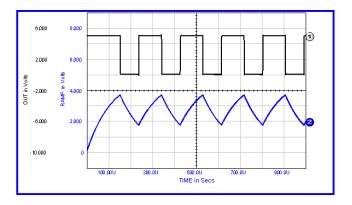

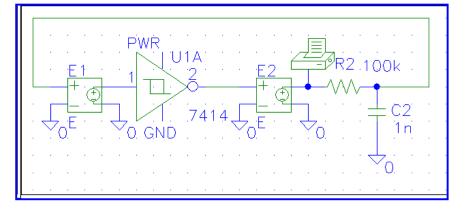

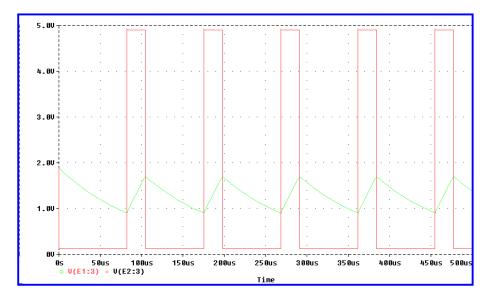

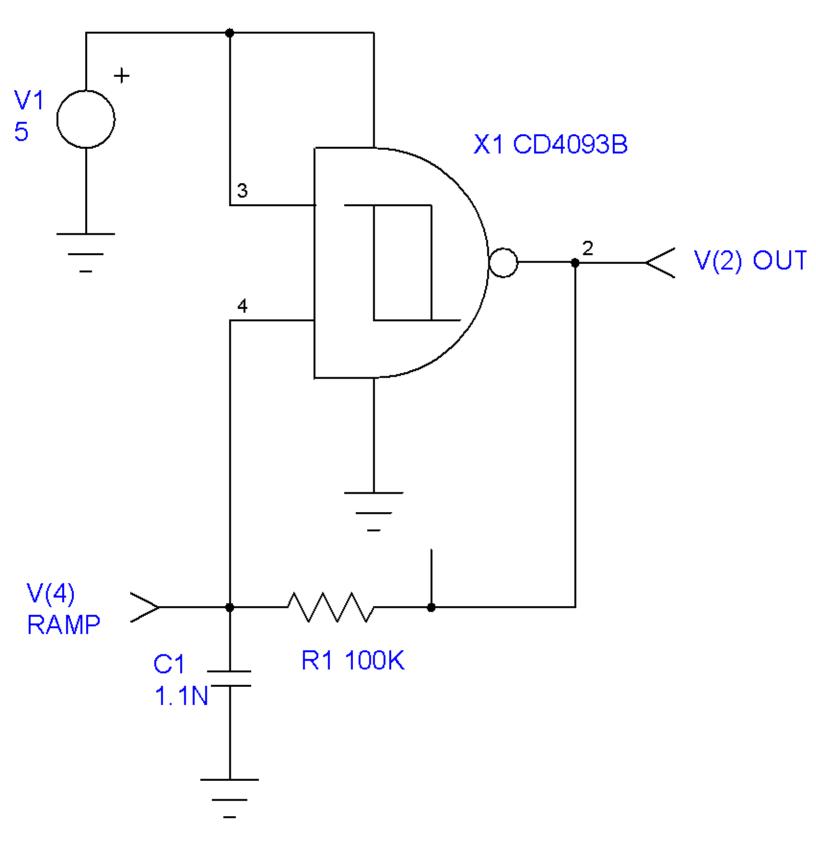

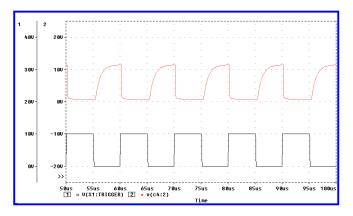

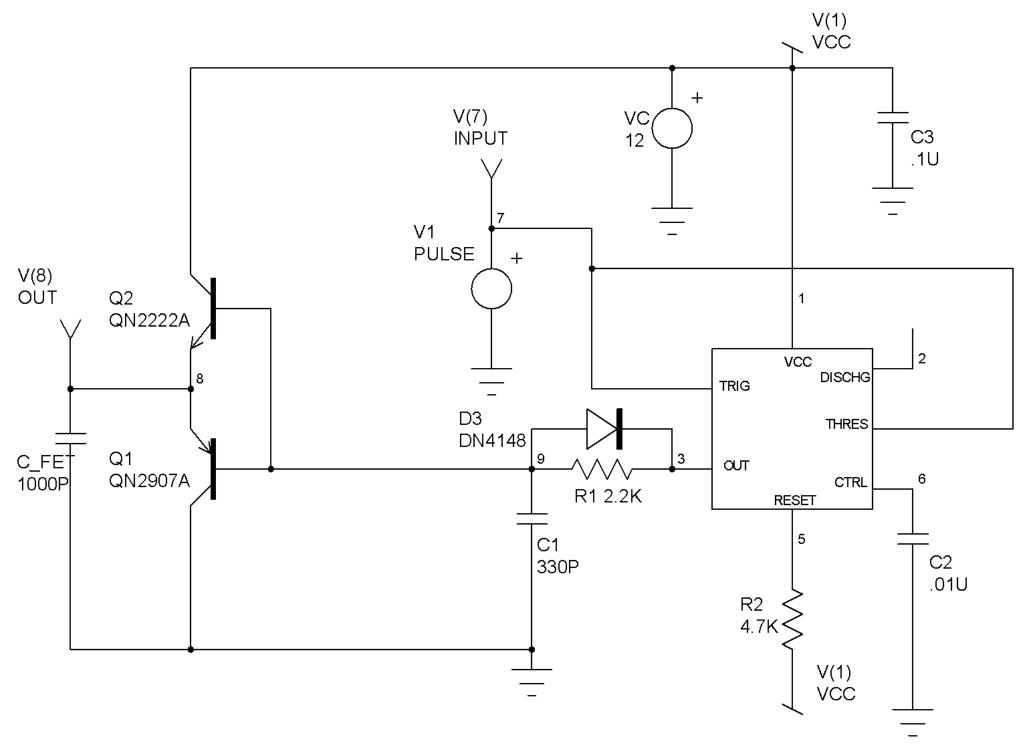

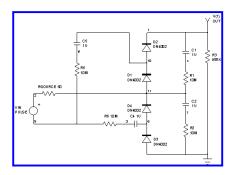

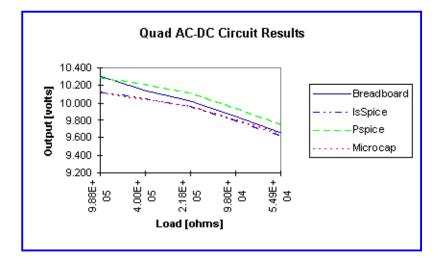

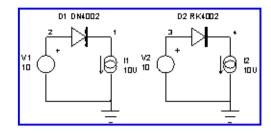

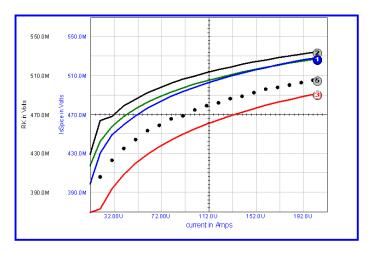

> Copyright 2002, PCBCafe. 1-888-44-WEB-44